无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

表 835-11-B4

编号: AiP8F3264-AX-J001

# AiP8F3264

## 64KB Flash ROM 的触摸型

### 8 位微控制器

#### 产品说明书

说明书发行履历:

| 版本         | 发行时间    | 新制/修订内容             |

|------------|---------|---------------------|

| 2021-09-A1 | 2021-09 | 新制                  |

| 2021-12-B1 | 2021-12 | 修改寄存器名称             |

| 2023-03-C1 | 2023-03 | 说明书模板更新             |

| 2023-05-D1 | 2023-05 | 添加 Flash/EEPROM 参数表 |

| 2023-06-D2 | 2023-06 | 修订                  |

| 2024-03-D3 | 2024-03 | 参数修正                |

| 2024-05-D4 | 2024-05 | LCD 功能说明修改          |

| 2024-06-D5 | 2024-06 | 内容修订                |

| 2025-02-D6 | 2025-02 | 引脚排列图修订             |

| 2025-05-D7 | 2025-05 | 内容修订                |

## 目录

|                         |    |

|-------------------------|----|

| 1 概述 .....              | 9  |

| 1.1 说明 .....            | 9  |

| 1.2 特性 .....            | 9  |

| 1.3 订购信息 .....          | 10 |

| 1.4 使用注意事项 .....        | 10 |

| 2 功能框图及引脚说明 .....       | 11 |

| 2.1 功能框图 .....          | 11 |

| 2.2 引脚排列图 .....         | 12 |

| 2.3 引脚说明 .....          | 15 |

| 3 电气特性 .....            | 17 |

| 3.1 极限参数 .....          | 17 |

| 3.2 工作电压-频率 .....       | 17 |

| 3.3 DC 特性 .....         | 18 |

| 3.4 上电复位特性 .....        | 18 |

| 3.5 LVR&LVD 电气特性 .....  | 19 |

| 3.6 内部高速 RC 振荡器特性 ..... | 20 |

| 3.7 内部低速 RC 振荡器特性 ..... | 20 |

| 3.8 ADC 电气特性 .....      | 20 |

| 3.9 OPA 电气特性 .....      | 21 |

| 3.10 CMP 电气特性 .....     | 21 |

| 3.11 LCD 电气特性 .....     | 21 |

| 3.12 LXT 电气特性 .....     | 22 |

| 3.13 AC 特性参数 .....      | 22 |

| 3.14 Flash 存储器参数 .....  | 22 |

| 4 存储器 .....             | 23 |

| 4.1 IAP 寄存器列表 .....     | 23 |

| 4.2 IAP 寄存器说明 .....     | 24 |

| 4.3 程序存储器 .....         | 27 |

| 4.3.1 FLASH 页擦除 .....   | 27 |

| 4.3.2 FLASH 编程 .....    | 28 |

|       |            |    |

|-------|------------|----|

| 4.3.3 | FLASH 读取   | 29 |

| 4.4   | 数据存储器      | 29 |

| 4.4.1 | 通用寄存器      | 29 |

| 4.4.2 | 位寻址空间      | 29 |

| 4.4.3 | 堆栈         | 30 |

| 4.4.4 | 特殊功能寄存器    | 30 |

| 4.4.5 | 系统控制寄存器    | 31 |

| 4.4.6 | 扩展地址寄存器    | 33 |

| 4.5   | EEPROM     | 34 |

| 4.5.1 | EEPROM 区擦除 | 34 |

| 4.5.2 | EEPROM 写入  | 35 |

| 4.5.3 | EEPROM 读取  | 36 |

| 5     | 时钟         | 37 |

| 5.1   | 特性         | 37 |

| 5.2   | 功能框图       | 37 |

| 5.3   | 寄存器列表      | 37 |

| 5.4   | 寄存器说明      | 38 |

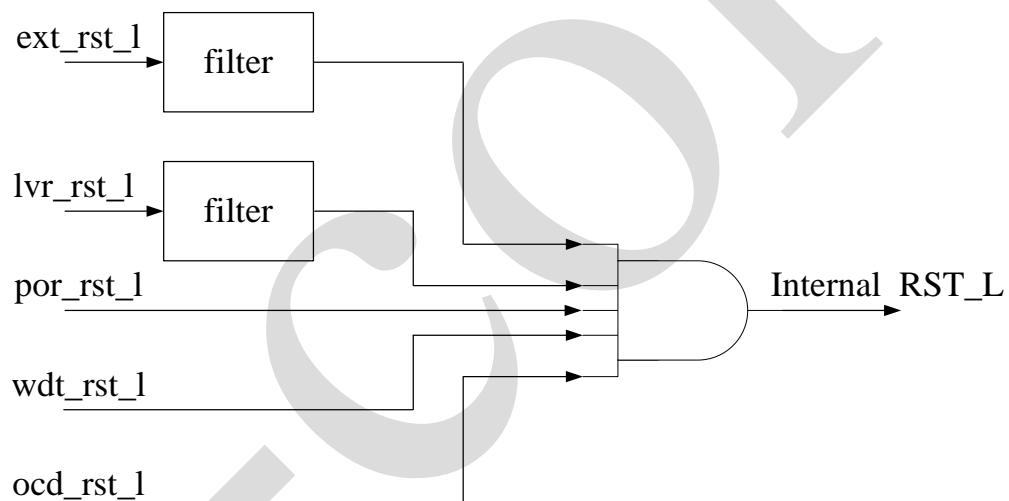

| 6     | 复位         | 41 |

| 6.1   | 特性         | 41 |

| 6.2   | 功能框图       | 41 |

| 6.3   | 寄存器列表      | 41 |

| 6.4   | 寄存器说明      | 42 |

| 7     | 工作模式       | 44 |

| 7.1   | 特性         | 44 |

| 7.2   | 寄存器列表      | 44 |

| 7.3   | 寄存器说明      | 45 |

| 8     | 中断         | 47 |

| 8.1   | 特性         | 47 |

| 8.2   | 中断源和中断向量   | 47 |

| 8.3   | 中断优先级      | 48 |

| 8.4   | 寄存器列表      | 49 |

|                         |            |

|-------------------------|------------|

| 8.5 寄存器说明 .....         | 49         |

| <b>9 GPIO .....</b>     | <b>56</b>  |

| 9.1 特性 .....            | 56         |

| 9.2 寄存器列表 .....         | 56         |

| 9.3 寄存器说明 .....         | 57         |

| <b>10 通用定时器 .....</b>   | <b>75</b>  |

| 10.1 特性 .....           | 75         |

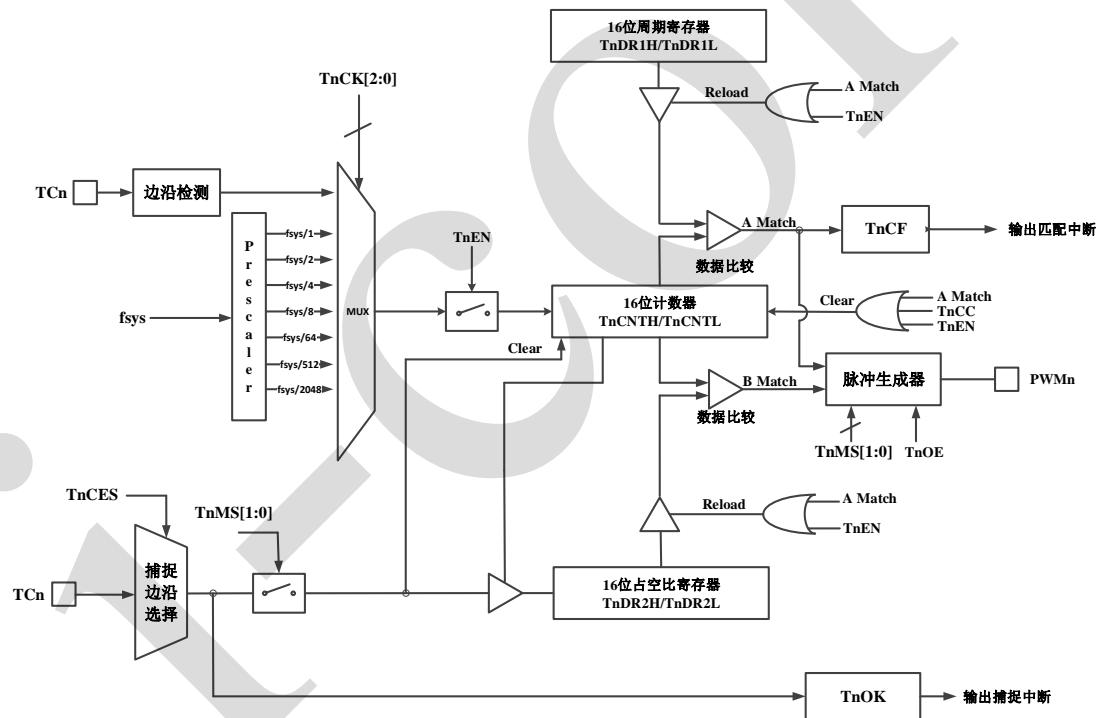

| 10.2 功能框图 .....         | 75         |

| 10.3 寄存器列表 .....        | 76         |

| 10.4 寄存器说明 .....        | 76         |

| 10.5 功能说明 .....         | 79         |

| 10.5.1 时钟选择 .....       | 79         |

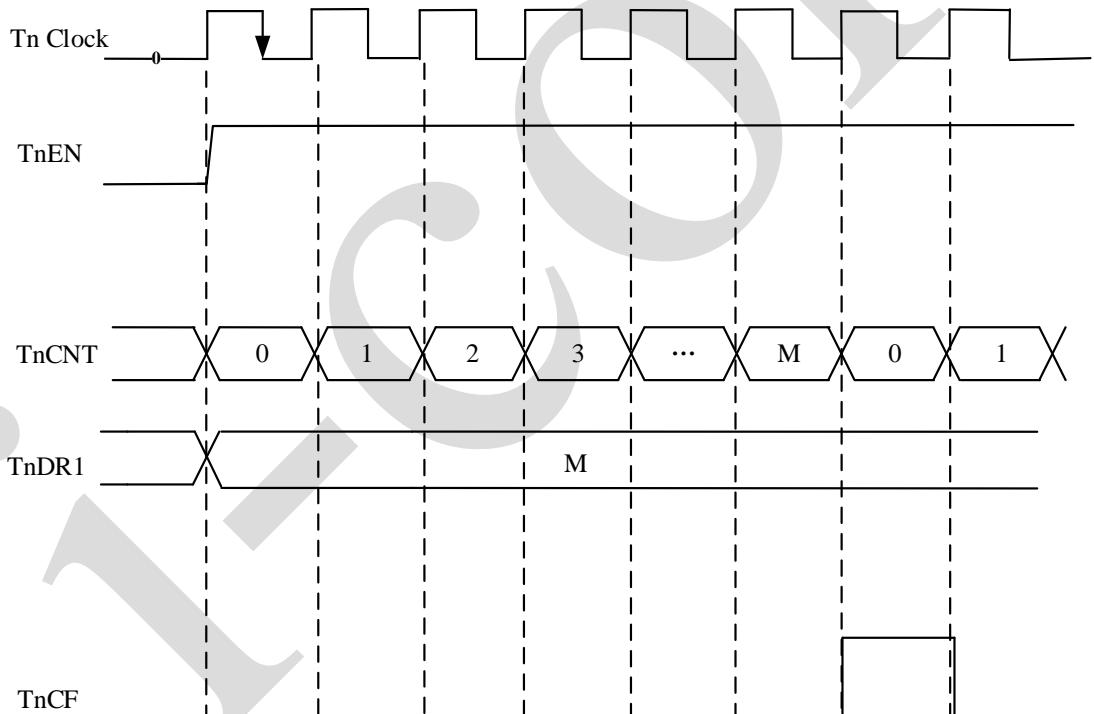

| 10.5.2 定时器/计数模式 .....   | 79         |

| 10.5.3 捕捉模式 .....       | 81         |

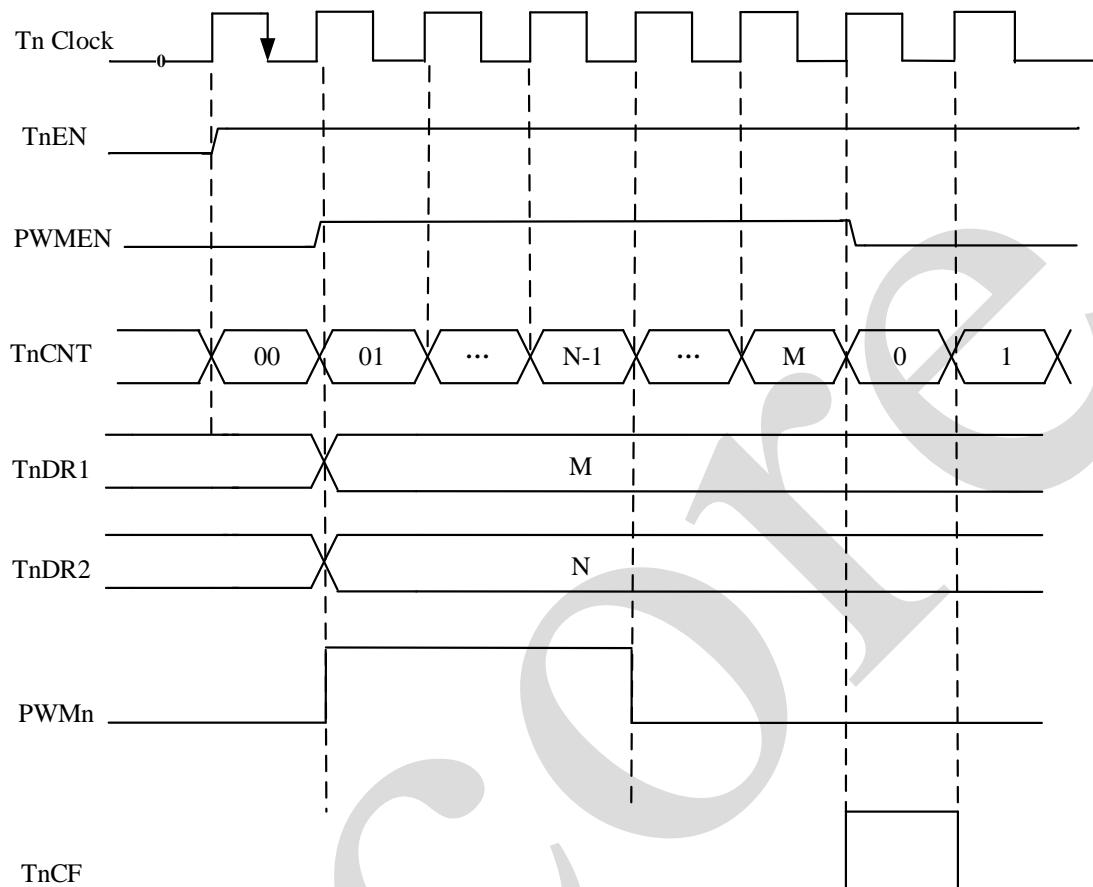

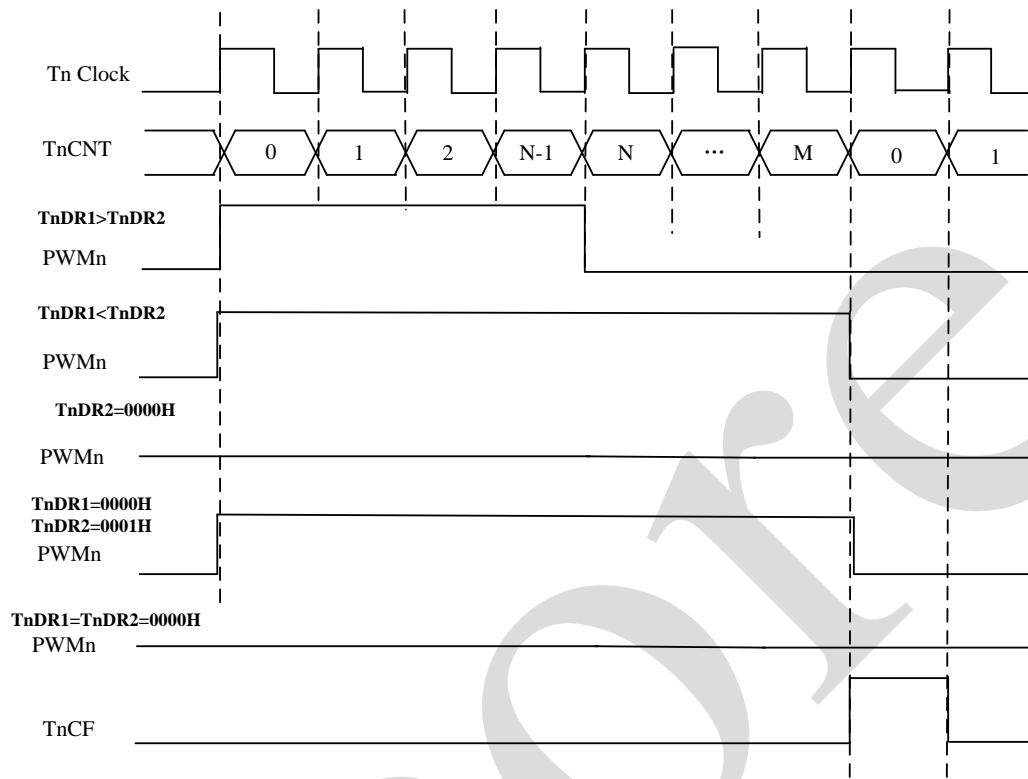

| 10.5.4 单脉冲 PWM 模式 ..... | 84         |

| 10.5.5 多脉冲 PWM 模式 ..... | 88         |

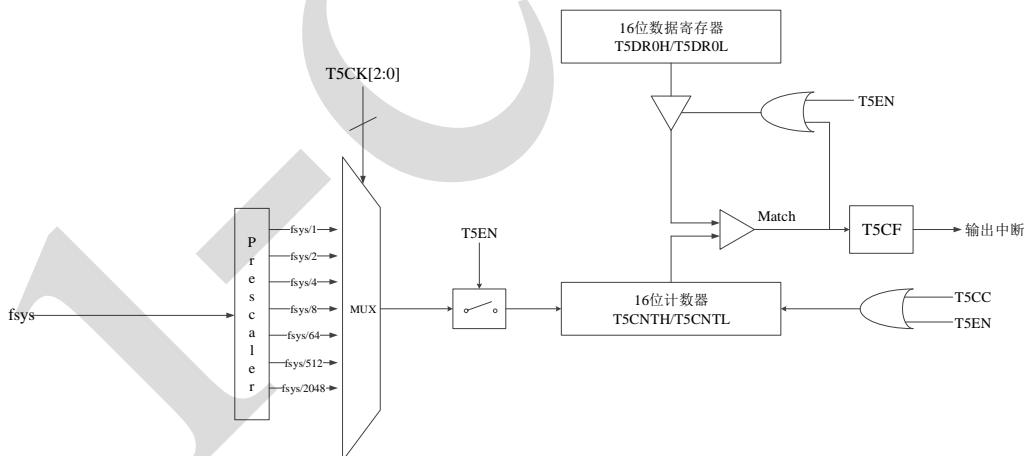

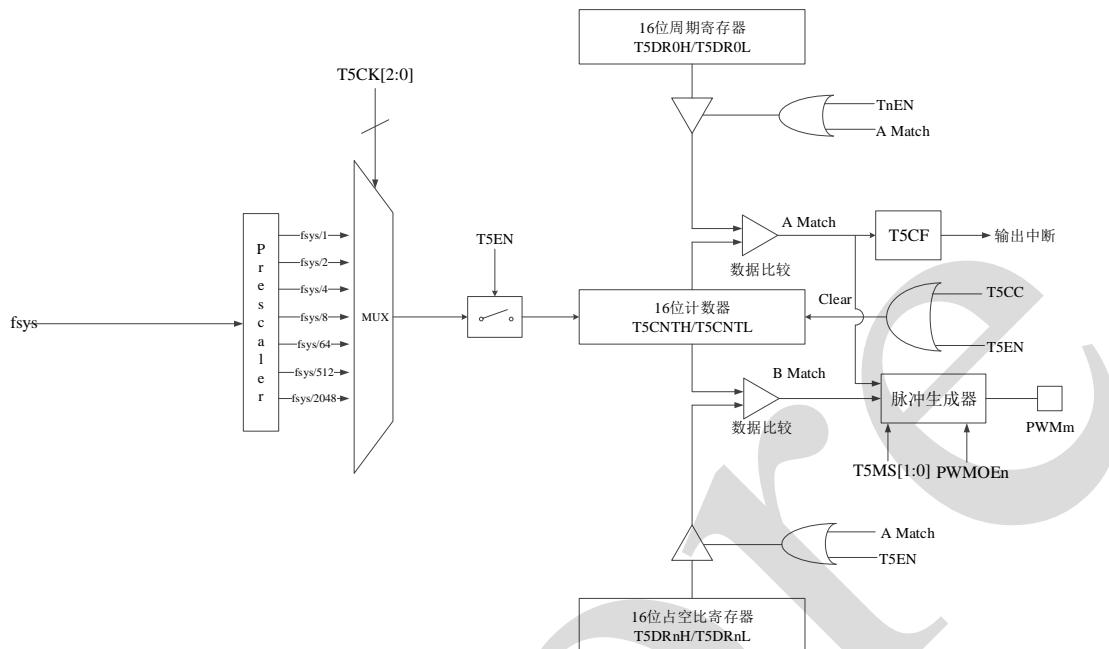

| <b>11 高级定时器 .....</b>   | <b>89</b>  |

| 11.1 特性 .....           | 89         |

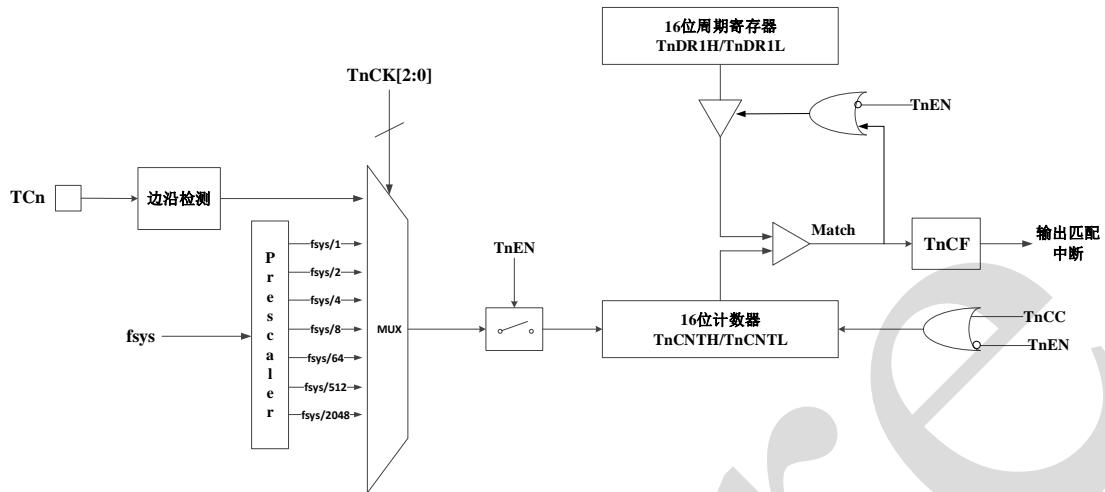

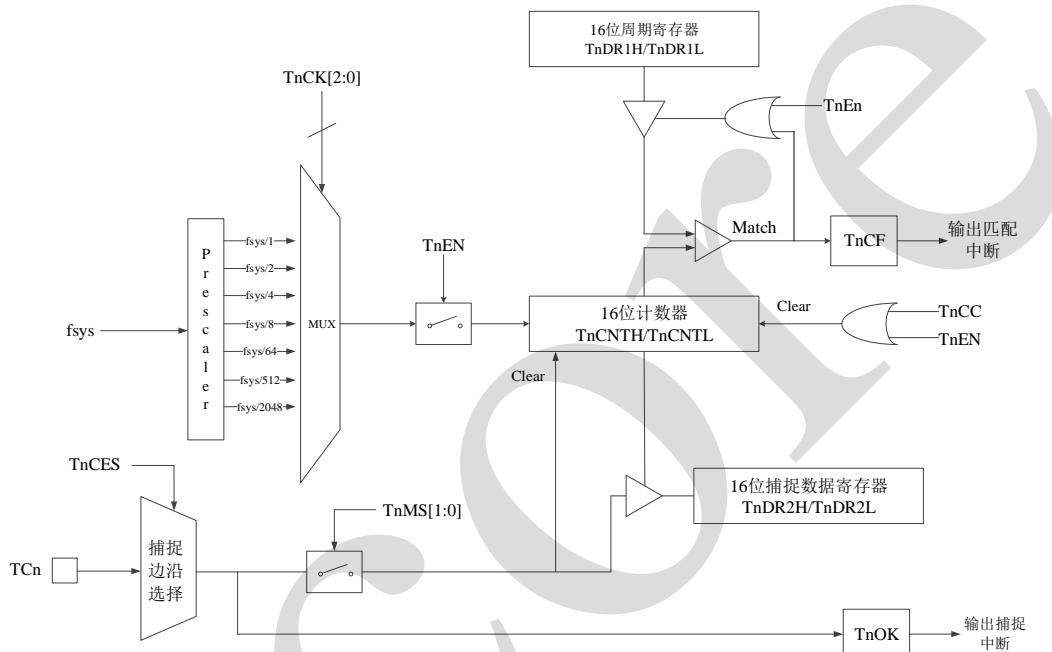

| 11.2 功能框图 .....         | 89         |

| 11.3 寄存器列表 .....        | 90         |

| 11.4 寄存器说明 .....        | 91         |

| 11.5 功能说明 .....         | 99         |

| 11.5.1 时钟选择 .....       | 99         |

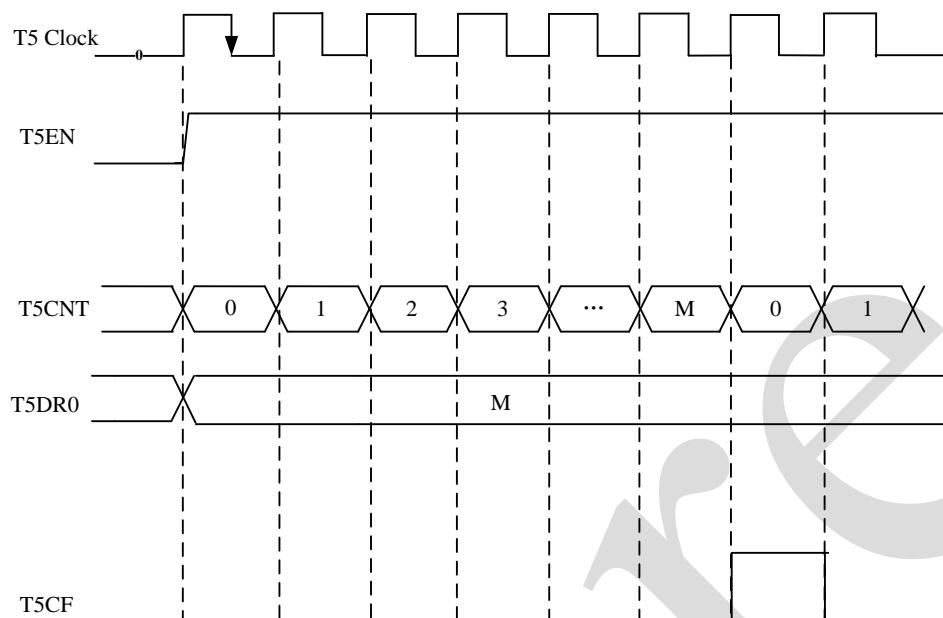

| 11.5.2 定时器/计数模式 .....   | 99         |

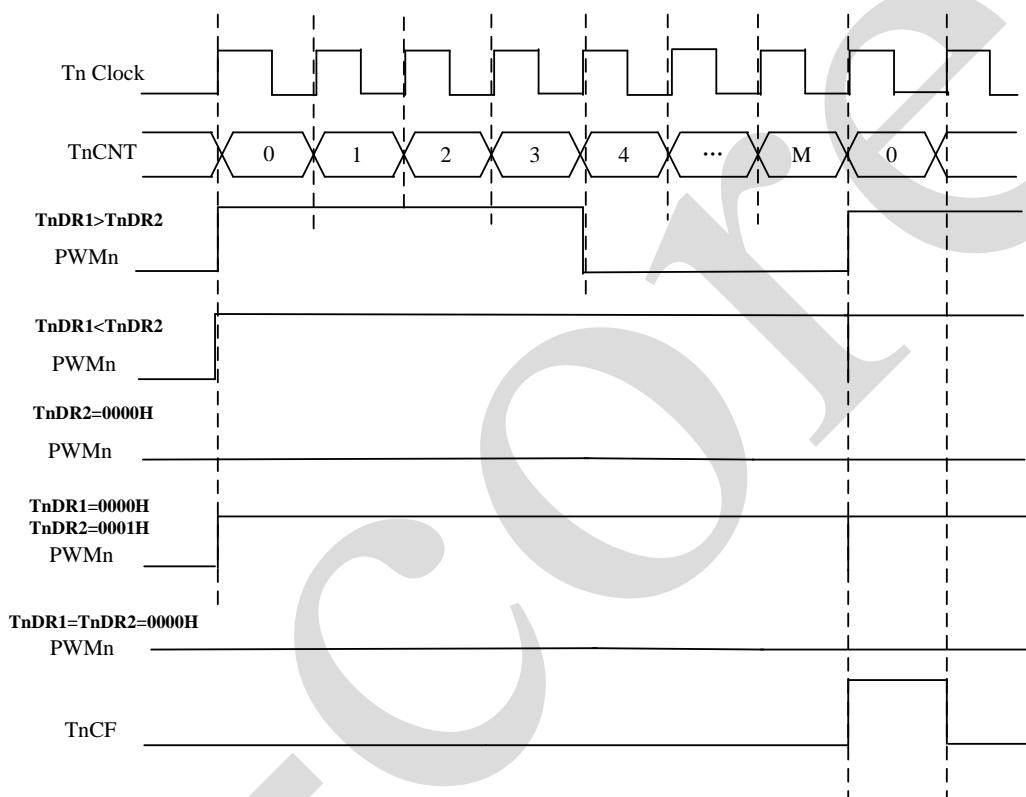

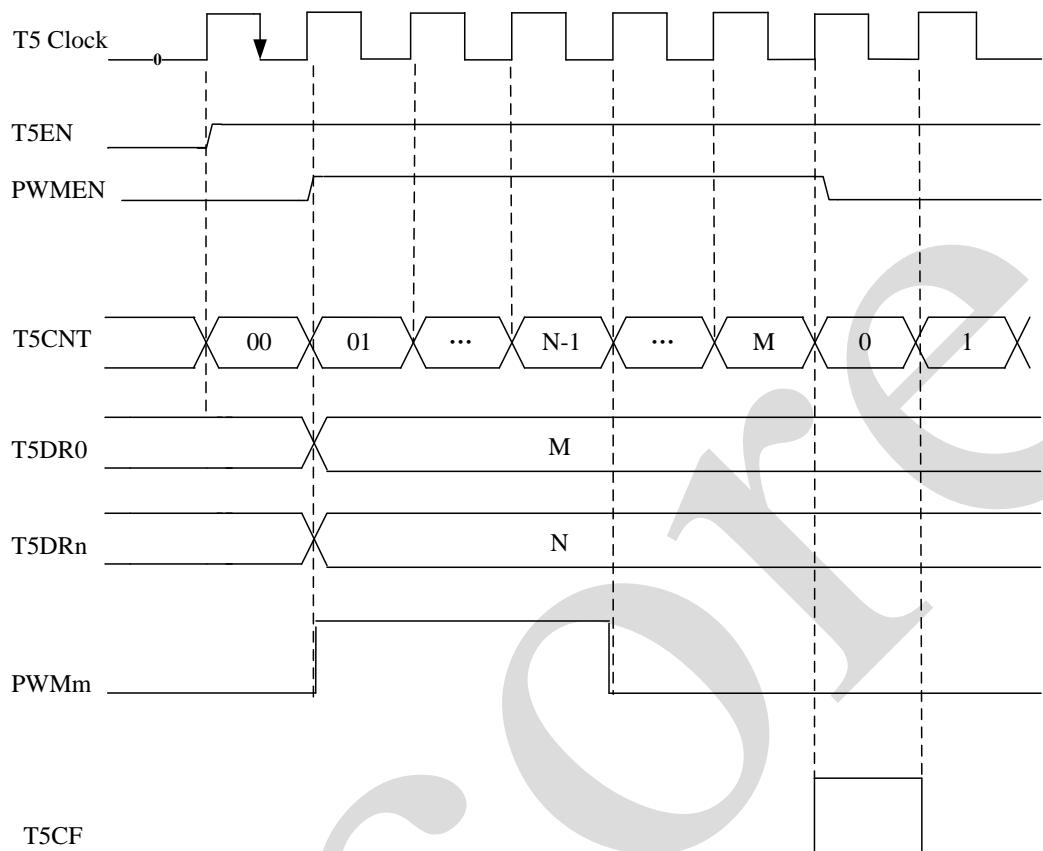

| 11.5.3 单脉冲 PWM 模式 ..... | 100        |

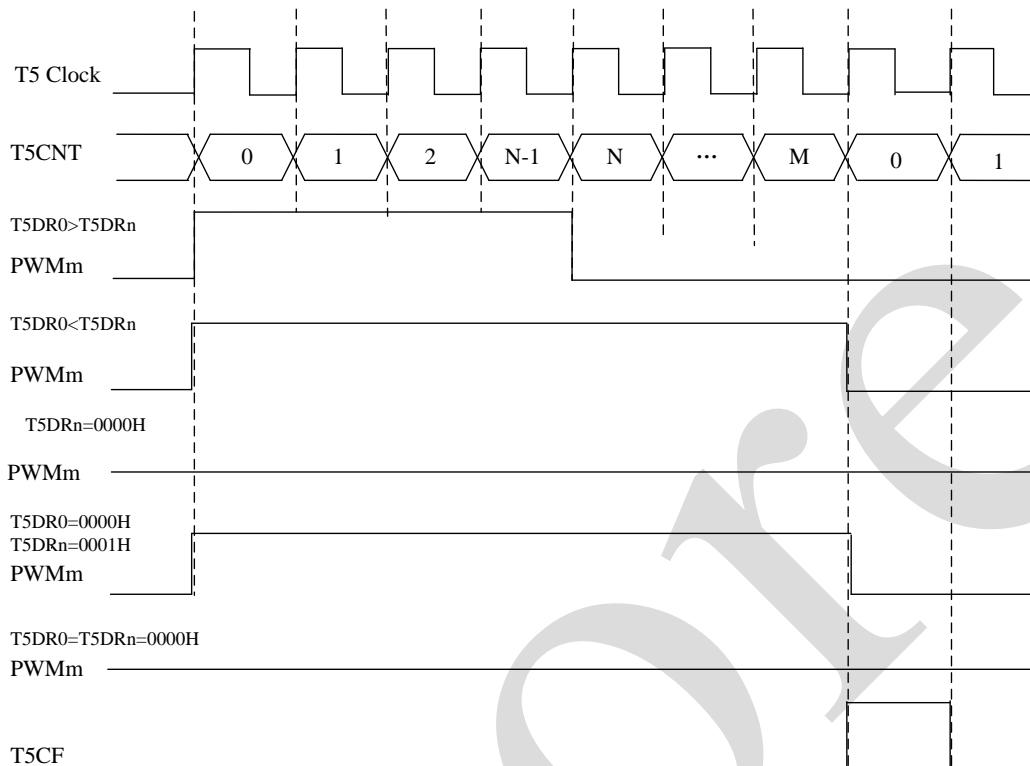

| 11.5.4 多脉冲 PWM 模式 ..... | 102        |

| 11.5.5 互补输出 .....       | 103        |

| 11.5.6 死区控制 .....       | 104        |

| <b>12 WT .....</b>      | <b>107</b> |

| 12.1 特性 .....           | 107        |

| 12.2 功能框图 .....         | 107        |

---

|                         |            |

|-------------------------|------------|

| 12.3 寄存器列表 .....        | 108        |

| 12.4 寄存器说明 .....        | 108        |

| 12.5 功能说明 .....         | 109        |

| 12.5.1 低 14 位计数模式 ..... | 109        |

| 12.5.2 高 8 位计数模式 .....  | 110        |

| <b>13 WDT .....</b>     | <b>111</b> |

| 13.1 特性 .....           | 111        |

| 13.2 功能框图 .....         | 111        |

| 13.3 寄存器列表 .....        | 111        |

| 13.4 寄存器说明 .....        | 112        |

| 13.5 功能说明 .....         | 114        |

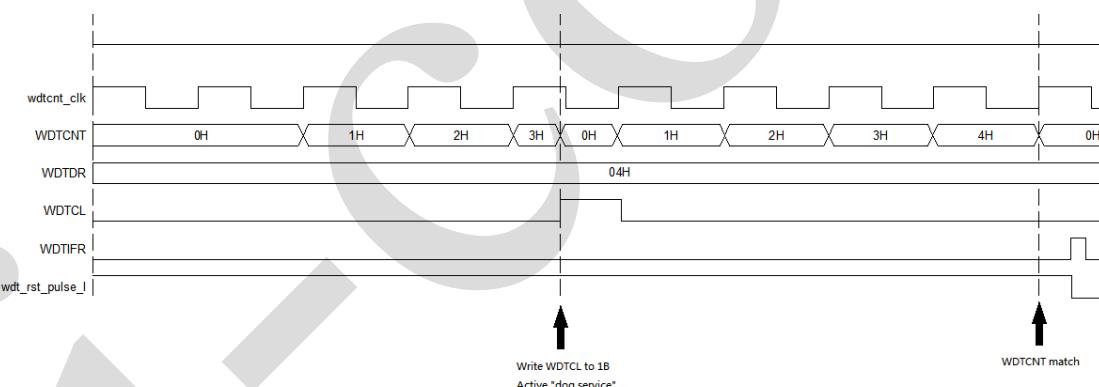

| 13.5.1 看门狗复位模式 .....    | 114        |

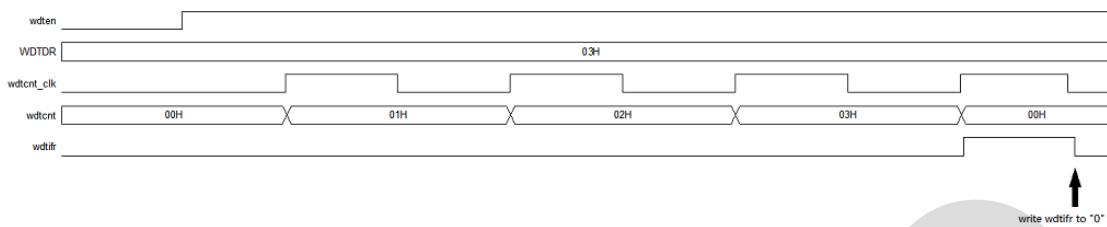

| 13.5.2 看门狗定时器模式 .....   | 115        |

| <b>14 UART .....</b>    | <b>116</b> |

| 14.1 特性 .....           | 116        |

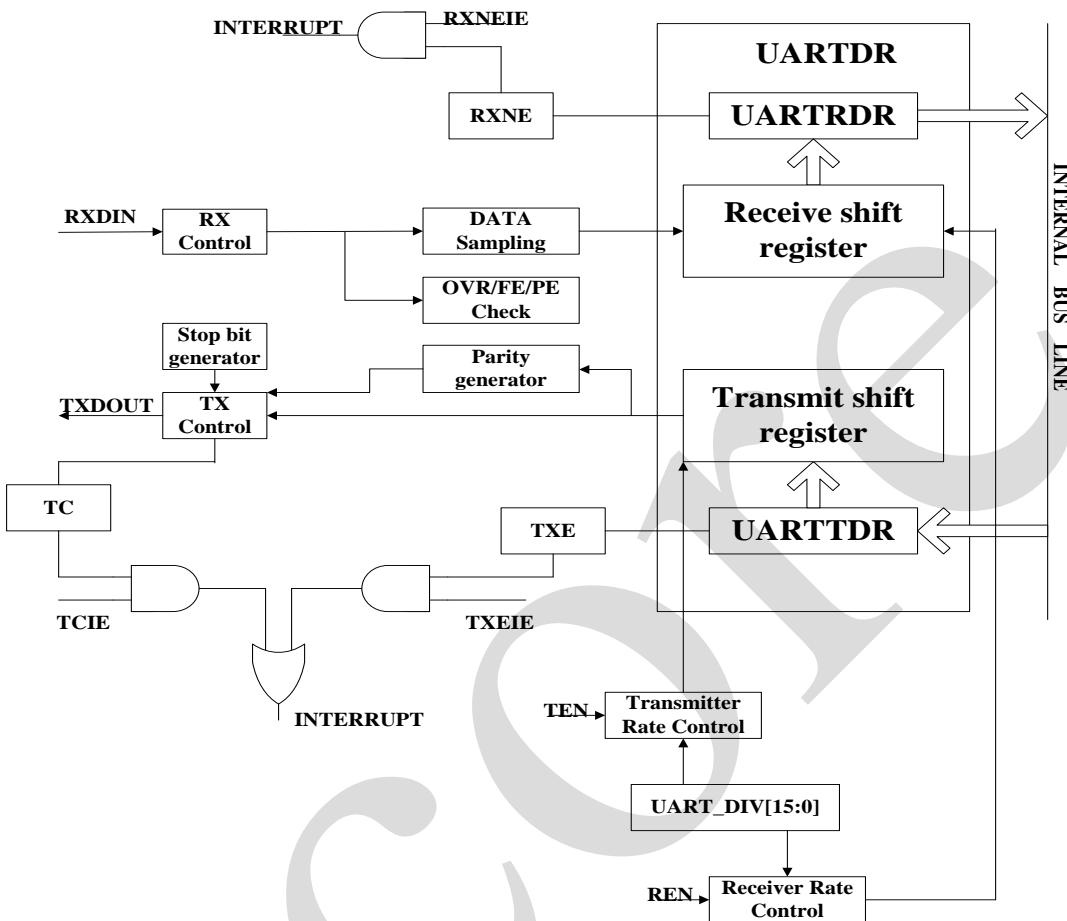

| 14.2 功能框图 .....         | 117        |

| 14.3 寄存器列表 .....        | 118        |

| 14.4 寄存器说明 .....        | 118        |

| 14.5 功能说明 .....         | 122        |

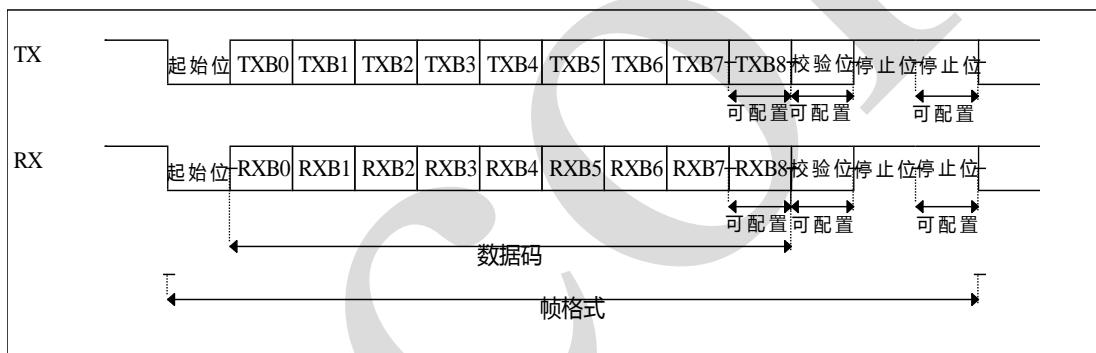

| 14.5.1 数据格式 .....       | 122        |

| 14.5.2 发送器 .....        | 122        |

| 14.5.3 接收器 .....        | 122        |

| 14.5.4 高精度波特率发生器 .....  | 123        |

| 14.5.5 奇偶校验 .....       | 124        |

| 14.5.6 多处理器通讯 .....     | 124        |

| 14.5.7 标志位 .....        | 124        |

| 14.5.8 中断 .....         | 125        |

| 14.5.9 软件复位功能 .....     | 125        |

| <b>15 SPI .....</b>     | <b>126</b> |

| 15.1 特性 .....           | 126        |

| 15.2 功能框图 .....         | 126        |

|                                    |            |

|------------------------------------|------------|

| 15.3 寄存器列表 .....                   | 127        |

| 15.4 寄存器说明 .....                   | 127        |

| 15.5 功能说明 .....                    | 130        |

| 15.5.1 数据收发 .....                  | 130        |

| 15.5.2 NSS 引脚管理 .....              | 131        |

| 15.5.3 SPI 标志位信号 .....             | 131        |

| 15.5.4 SPI 中断 .....                | 133        |

| <b>16 I2C .....</b>                | <b>134</b> |

| 16.1 特性 .....                      | 134        |

| 16.2 功能框图 .....                    | 135        |

| 16.3 寄存器列表 .....                   | 136        |

| 16.4 寄存器说明 .....                   | 136        |

| 16.5 功能说明 .....                    | 140        |

| 16.5.1 工作方式 .....                  | 140        |

| 16.5.2 模式选择 .....                  | 140        |

| 16.5.3 通信过程 .....                  | 141        |

| 16.5.4 通信协议 .....                  | 141        |

| 16.5.5 时钟同步和总线仲裁 .....             | 141        |

| 16.5.6 START/STOP 信号 .....         | 143        |

| 16.5.7 时钟发生器 .....                 | 143        |

| 16.5.8 主机发送 .....                  | 144        |

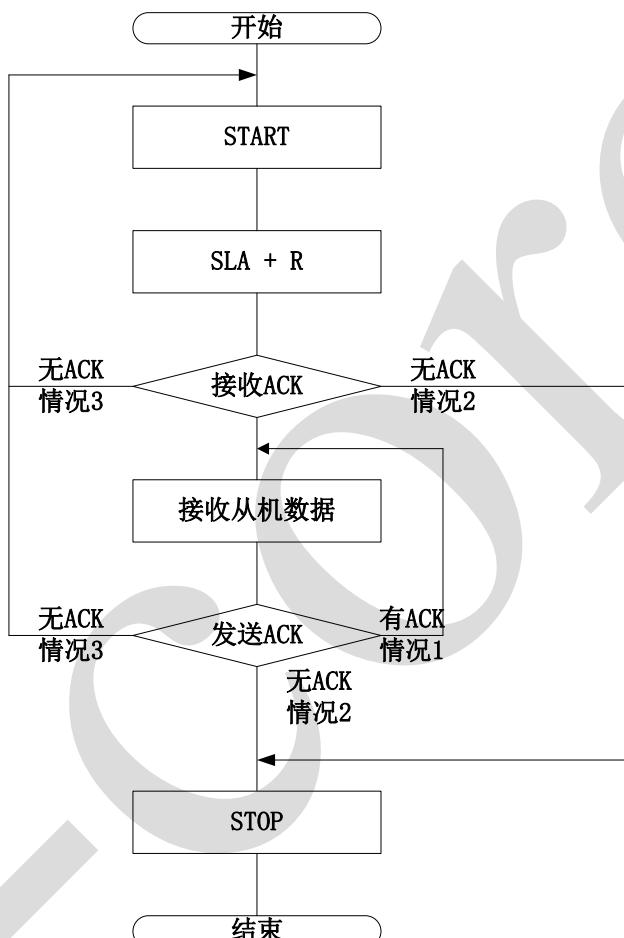

| 16.5.9 主机接收 .....                  | 146        |

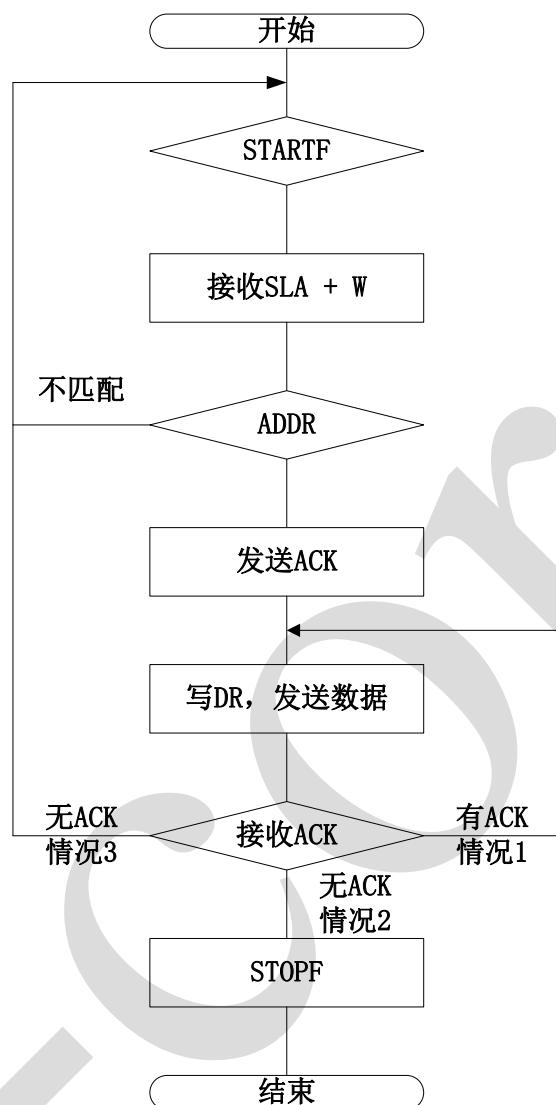

| 16.5.10 从机发送 .....                 | 148        |

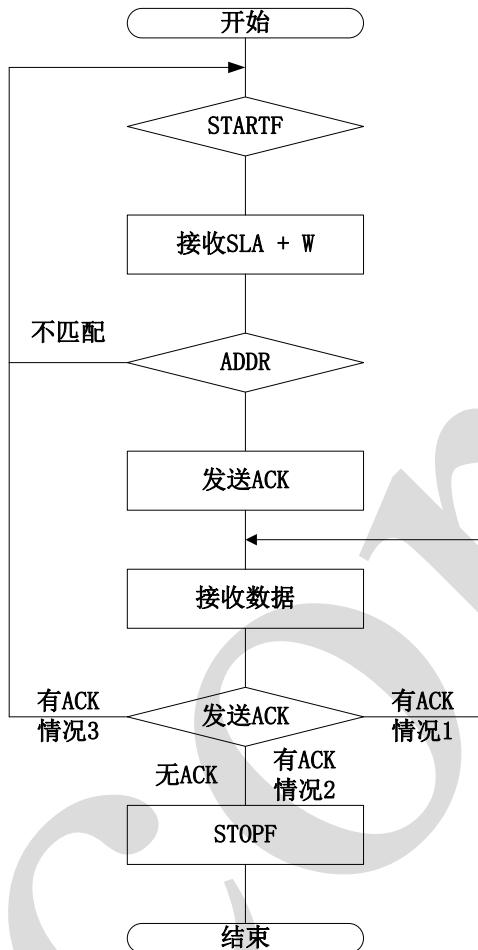

| 16.5.11 从机接收 .....                 | 150        |

| 16.5.12 I2C 状态标志 .....             | 152        |

| 16.5.13 I2C 错误标志 .....             | 154        |

| 16.5.14 广播呼叫功能 .....               | 154        |

| 16.5.15 SDA 数据在 SCL 下降沿后保持功能 ..... | 154        |

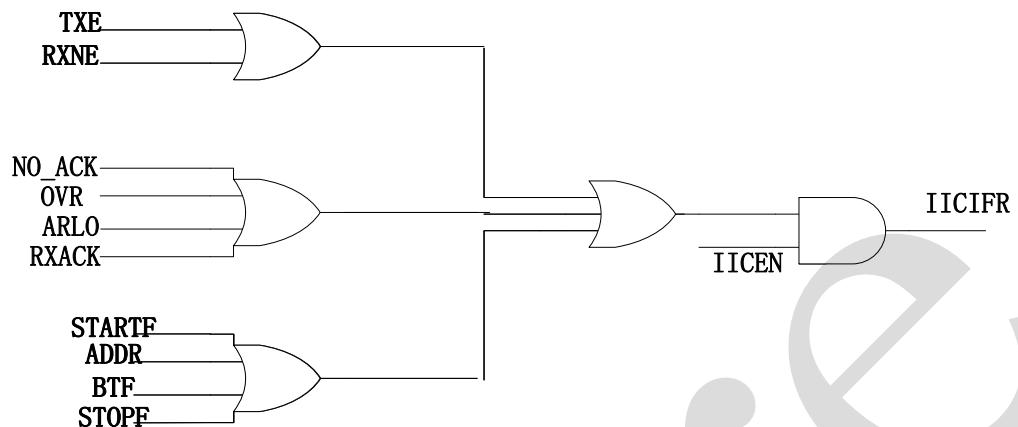

| 16.5.16 中断 .....                   | 155        |

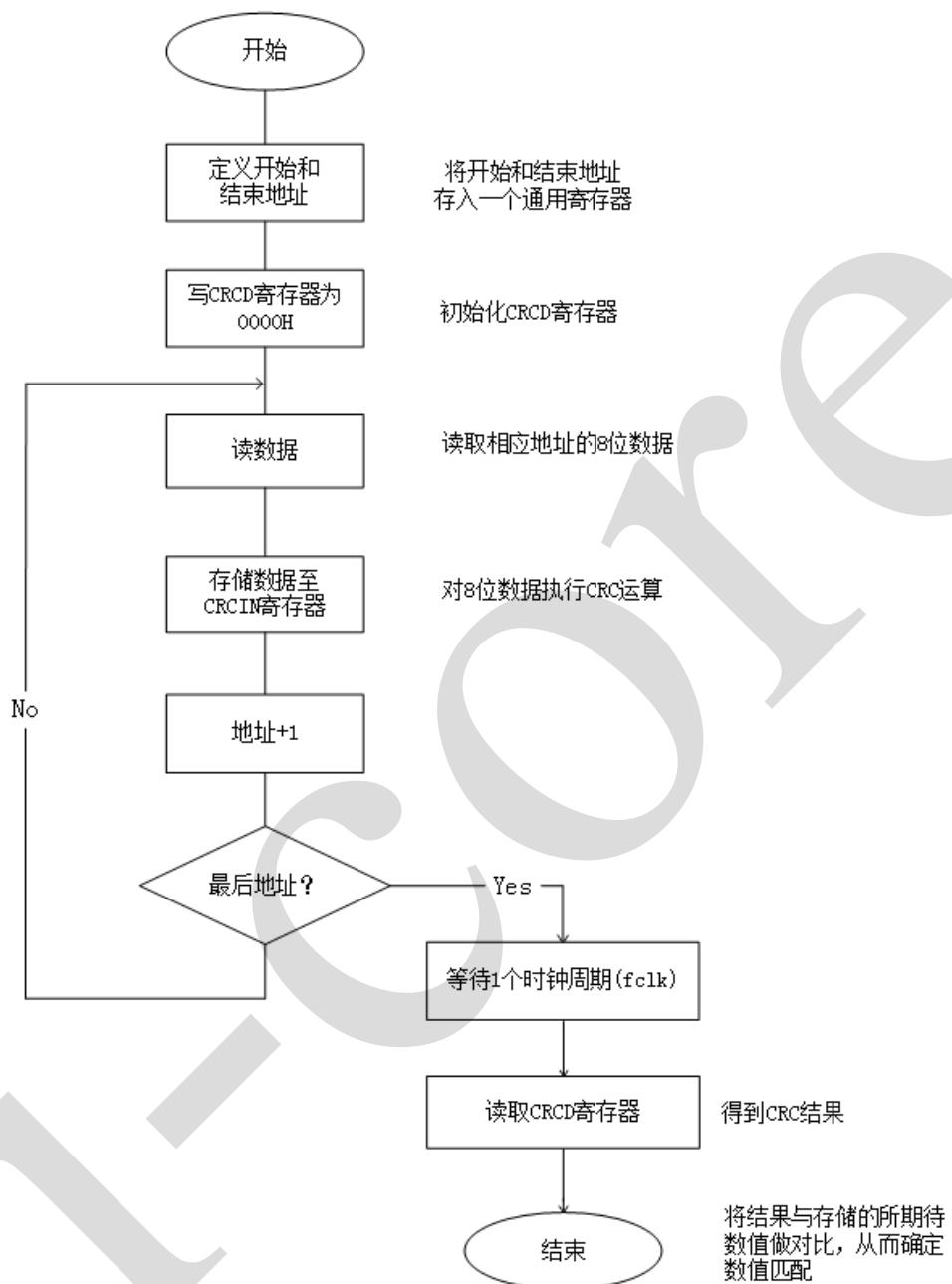

| <b>17 CRC .....</b>                | <b>156</b> |

| 17.1 特性 .....                      | 156        |

---

|           |                 |            |

|-----------|-----------------|------------|

| 17.2      | 流程框图            | 157        |

| 17.3      | 寄存器列表           | 158        |

| 17.4      | 寄存器说明           | 158        |

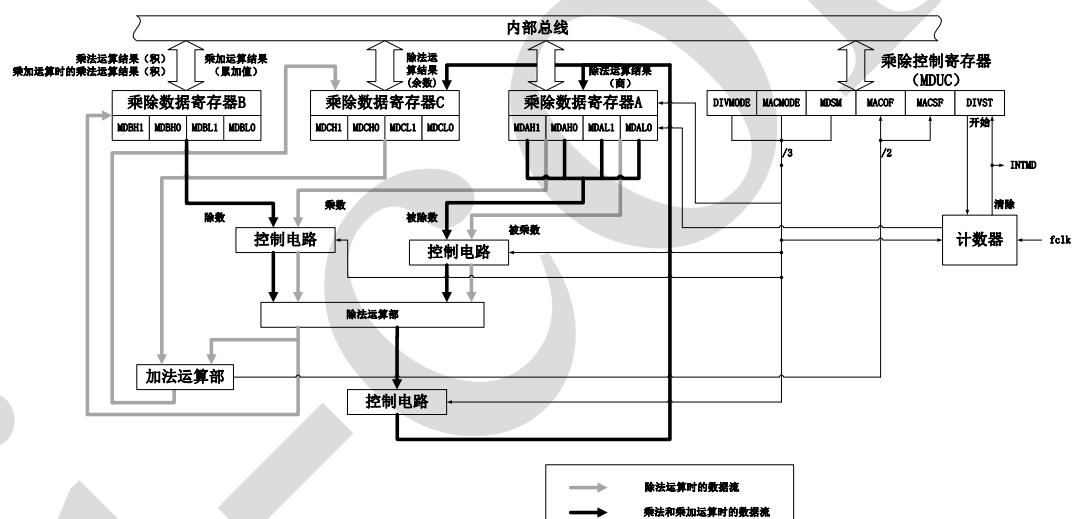

| <b>18</b> | <b>MDU</b>      | <b>159</b> |

| 18.1      | 特性              | 159        |

| 18.2      | 功能框图            | 159        |

| 18.3      | 寄存器列表           | 160        |

| 18.4      | 寄存器说明           | 160        |

| 18.5      | 功能说明            | 164        |

| 18.5.1    | 16bit 无符号乘法运算   | 164        |

| 18.5.2    | 16bit 带符号乘法运算   | 165        |

| 18.5.3    | 16bit 无符号乘加运算   | 166        |

| 18.5.4    | 16bit 带符号乘加运算   | 166        |

| 18.5.5    | 32 位无符号除法运算     | 167        |

| 18.5.6    | 中断 (MDUIF)      | 167        |

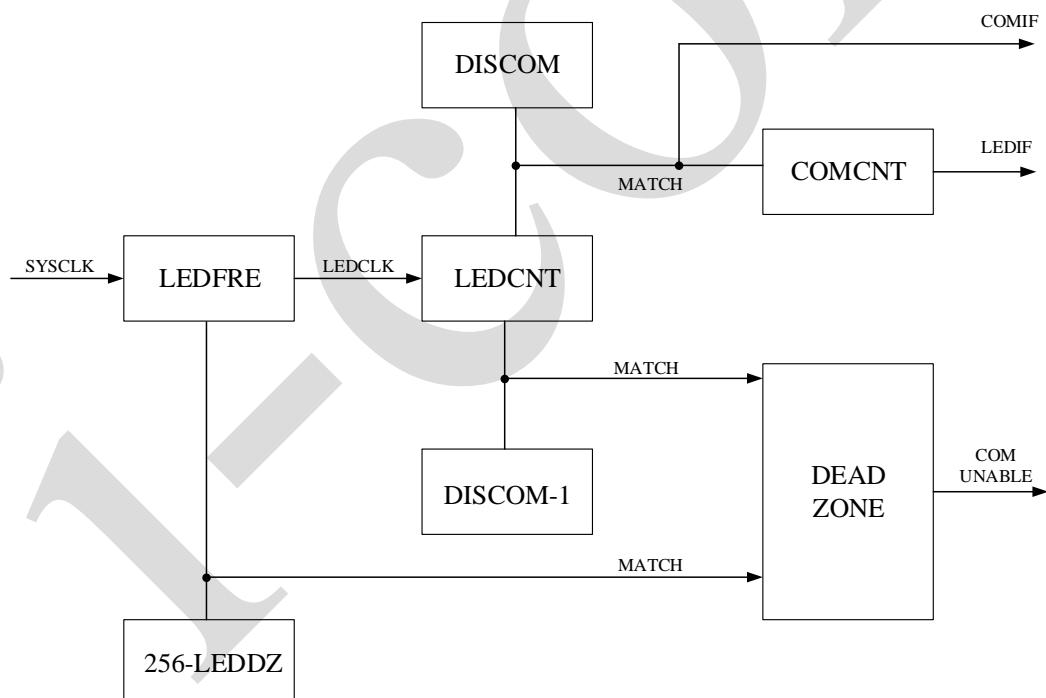

| <b>19</b> | <b>LED</b>      | <b>168</b> |

| 19.1      | 特性              | 168        |

| 19.2      | 原理框图            | 168        |

| 19.3      | 寄存器列表           | 169        |

| 19.4      | 寄存器说明           | 169        |

| 19.5      | 功能说明            | 170        |

| 19.5.1    | 模式 1: 亮灭 LED 模式 | 170        |

| 19.5.2    | 模式 2: 调光模式      | 171        |

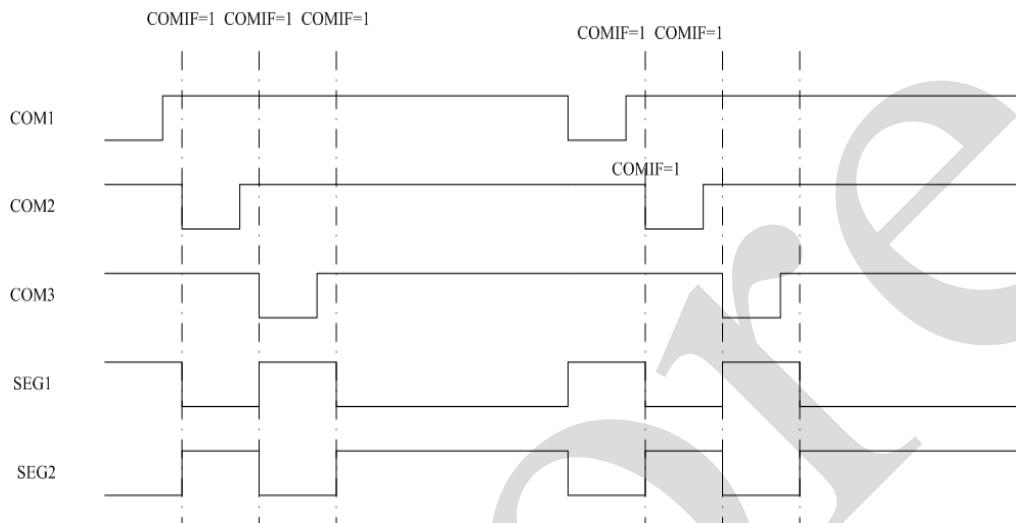

| <b>20</b> | <b>LCD</b>      | <b>174</b> |

| 20.1      | 特性              | 174        |

| 20.2      | 功能框图            | 174        |

| 20.3      | 寄存器列表           | 175        |

| 20.4      | 寄存器说明           | 175        |

| 20.5      | 功能说明            | 177        |

| 20.5.1    | LCD 大小选择        | 177        |

| 20.5.2    | 占空比调节           | 177        |

|                               |            |

|-------------------------------|------------|

| 20.5.3 帧频选择 .....             | 178        |

| 20.5.4 偏置电压选择 .....           | 178        |

| 20.5.5 偏置电阻选择 .....           | 178        |

| 20.5.6 快速充电模式 .....           | 178        |

| 20.5.7 充电周期 .....             | 179        |

| <b>21 TOUCH.....</b>          | <b>181</b> |

| <b>22 AD.....</b>             | <b>182</b> |

| 22.1 特性.....                  | 182        |

| 22.2 功能框图.....                | 182        |

| 22.3 寄存器列表.....               | 183        |

| 22.4 寄存器说明.....               | 183        |

| <b>23 OPA&amp;CMP.....</b>    | <b>186</b> |

| 23.1 特性.....                  | 186        |

| 23.2 寄存器列表.....               | 186        |

| 23.3 寄存器说明.....               | 186        |

| <b>24 LVD .....</b>           | <b>187</b> |

| 24.1 特性.....                  | 187        |

| 24.2 功能框图.....                | 187        |

| 24.3 寄存器列表.....               | 187        |

| 24.4 寄存器说明.....               | 188        |

| <b>25 封装尺寸与外形图 .....</b>      | <b>189</b> |

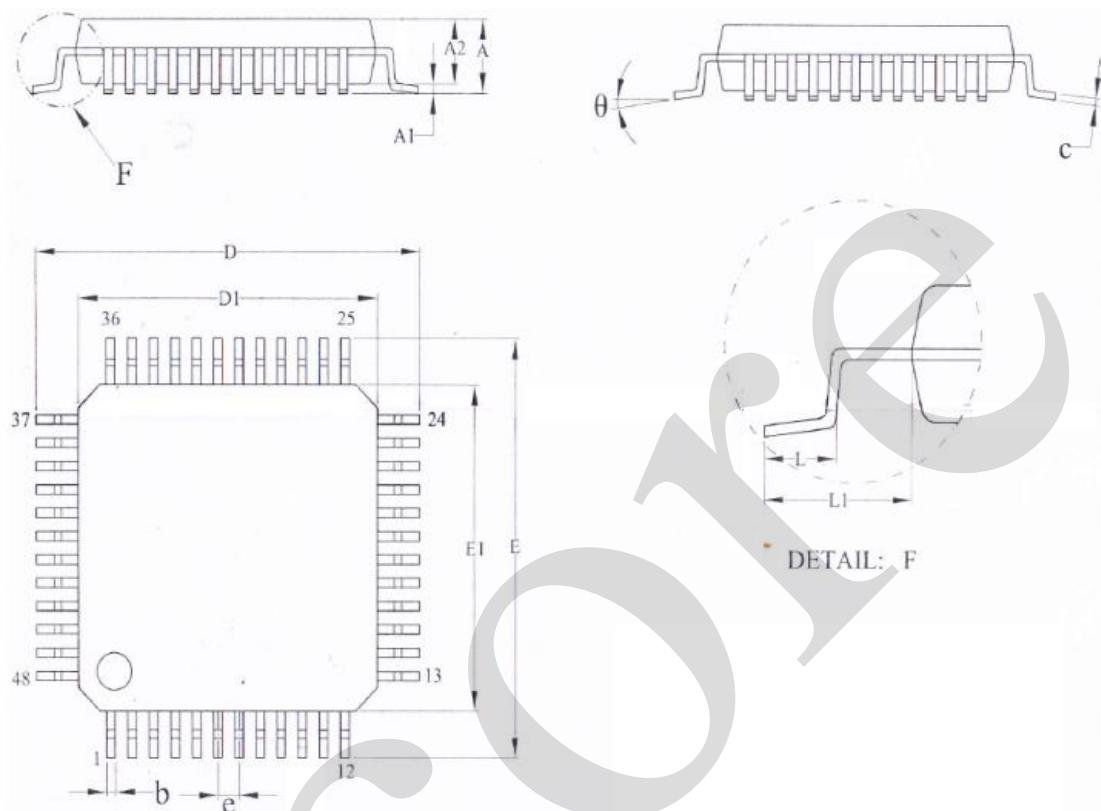

| 25.1 LQFP48 外形图与封装尺寸 .....    | 189        |

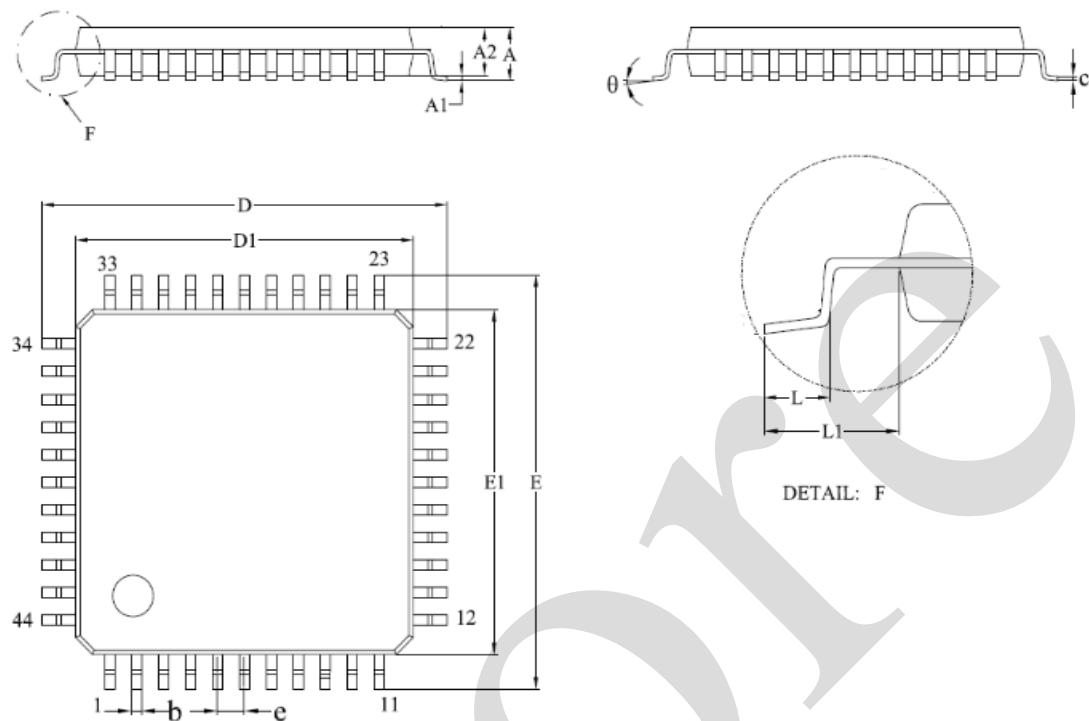

| 25.2 LQFP44 外形图与封装尺寸 .....    | 190        |

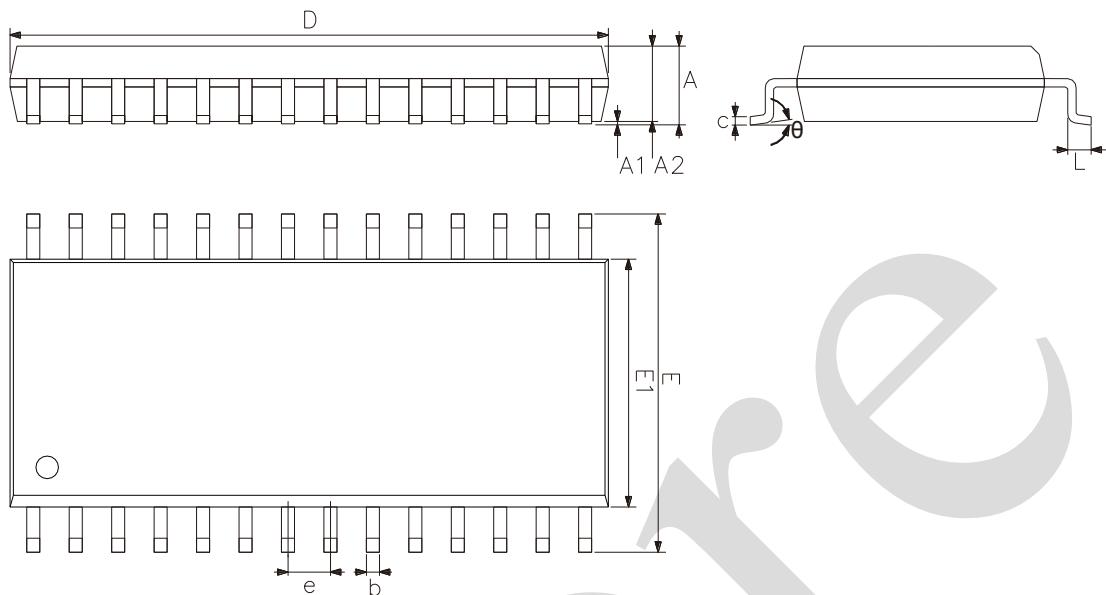

| 25.3 SOP28 外形图与封装尺寸 .....     | 191        |

| <b>26 声明及注意事项 .....</b>       | <b>192</b> |

| 26.1 产品中有毒有害物质或元素的名称及含量 ..... | 192        |

| 26.2 注意.....                  | 192        |

## 1 概述

### 1.1 说明

AiP8F3264 是一款触摸型 8051 内核 MCU，64KB FLASH ROM、2KB XRAM、256B IRAM、1KB EEPROM，内部集成 Timer0/1/2/5，UART0/1/2、SPI、I2C、CRC、MDU、LCD、LED 和 TOUCH，OPA&CMP、12bit-ADC。

### 1.2 特性

**内核:** 1T 8051

**工作电压:** 1.8V~5.5V

**工作模式:**

- 普通模式 (RUN)

- 空闲模式 (IDLE)

- 停止模式 (STOP)

**存储器:**

- FLASH: 64KB

- EEPROM: 1KB

- RAM: 256B IRAM, 2KB XRAM

**时钟:**

- 内部高速振荡: 16MHz

- 内部低速振荡: 16kHz

- 外部高速晶体/陶瓷振荡:

4M~16MHz

- 外部低速晶体振荡: 32.768kHz

**低电压复位:**

- 14 level 选择 (1.90V~4.4V)

**低电压检测:**

- 13 level 选择 (2.0V~4.4V)

**中断:**

- 20 个外部中断源

- 17 个内部中断源

- 中断优先级软件设置

**GPIO:**

- 46 个多功能双向 I/O 口

- 支持独立弱上拉

- 8 个可复用 COM 口

- LED 驱动

- 高电平驱动能力, 10mA

- 低电平驱动能力, 30mA

**定时器:**

- 3 个 16 位通用定时器 T0/1/2

- 1 个 16 位高级定时器 T5

- Watch Dog Timer (WDT)

- Watch Timer (WT)

**通信接口:**

- 3 路 UART0/1/2

- 1 路 SPI

- 1 路 I2C

**CRC 校验模块**

**MDU 模块:** 乘法器/除法器, 支持最高

32 位除以 32 位无符号除法。

**显示驱动模块:**

- LCD 驱动

- 最大支持 24SEG 和 8 COM

- LED 驱动

- 最大支持 16SEG 和 8COM

**触摸模块:** 最多支持 31 个按键通道

**模拟外设:**

- OPA&CMP

- ADC

- 12 位 A/D 转换器, 最多支持 29

输入外部通道, 1/4VDD 通道。

- 内部 2V/3V/4V/VDD 基准

**工作温度:** -40°C ~ +105°C

**封装类型:**

- LQFP48/LQFP44

- SOP28

### 1.3 订购信息

管装:

| 产品料号               | 封装形式   | 打印标识        | 管装数          | 盒装管       | 盒装数           | 备注说明                                      |

|--------------------|--------|-------------|--------------|-----------|---------------|-------------------------------------------|

| AiP8F3264LA48.TB   | LQFP48 | AiP8F3264   | 250<br>PCS/板 | 10<br>板/盒 | 2500<br>PCS/盒 | 塑封体尺寸:<br>7.0mm×7.0mm<br>引脚间距:<br>0.5mm   |

| AiP8F3264LB44.TB   | LQFP44 | AiP8F3264   | 160<br>PCS/板 | 10<br>板/盒 | 1600<br>PCS/盒 | 塑封体尺寸:<br>10.0mm×10.0mm<br>引脚间距:<br>0.8mm |

| AiP8F3264-2LB44.TB | LQFP44 | AiP8F3264-2 | 160<br>PCS/板 | 10<br>板/盒 | 1600<br>PCS/盒 | 塑封体尺寸:<br>10.0mm×10.0mm<br>引脚间距:<br>0.8mm |

| AiP8F3264SA28.TB   | SOP28  | AiP8F3264   | 25<br>PCS/板  | 80<br>管/盒 | 2000<br>PCS/盒 | 塑封体尺寸:<br>17.9mm×7.5mm<br>引脚间距:<br>1.27mm |

编带:

| 产品料号             | 封装形式  | 打印标识      | 编带盘装数     | 编带盒装数     | 备注说明                                      |

|------------------|-------|-----------|-----------|-----------|-------------------------------------------|

| AiP8F3264SA28.TR | SOP28 | AiP8F3264 | 1250PCS/盘 | 1250PCS/盒 | 塑封体尺寸:<br>17.9mm×7.5mm<br>引脚间距:<br>1.27mm |

注: 订购信息与实物不符时, 以实物为准。

### 1.4 使用注意事项

如使用以下功能, 请参考《AiP8F3264 产品开发指南》

- 1、 中断优先级设置

- 2、 UART 发送中断设置

- 3、 WT 中断设置

软件注意事项:

1、 Flash 和 EEPROM 操作请参考说明书详细说明

## 2 功能框图及引脚说明

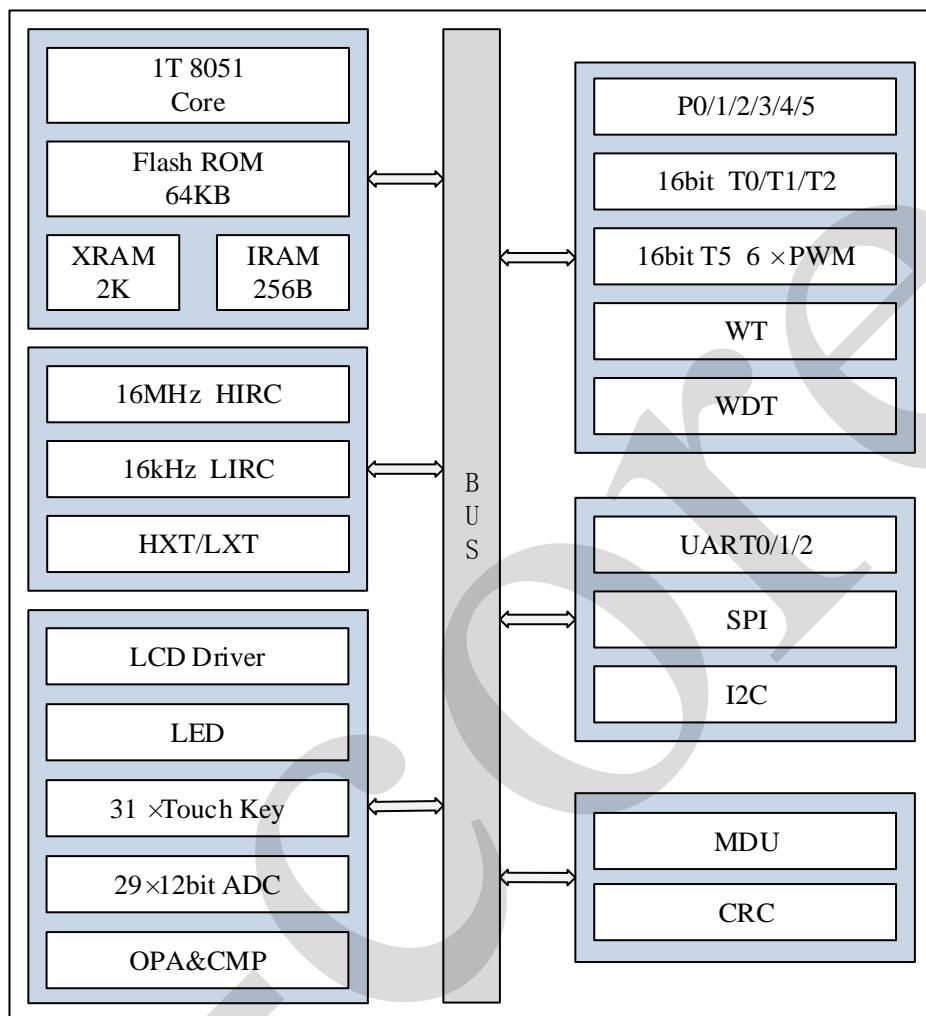

### 2.1 功能框图

图 2.1.1 功能框图

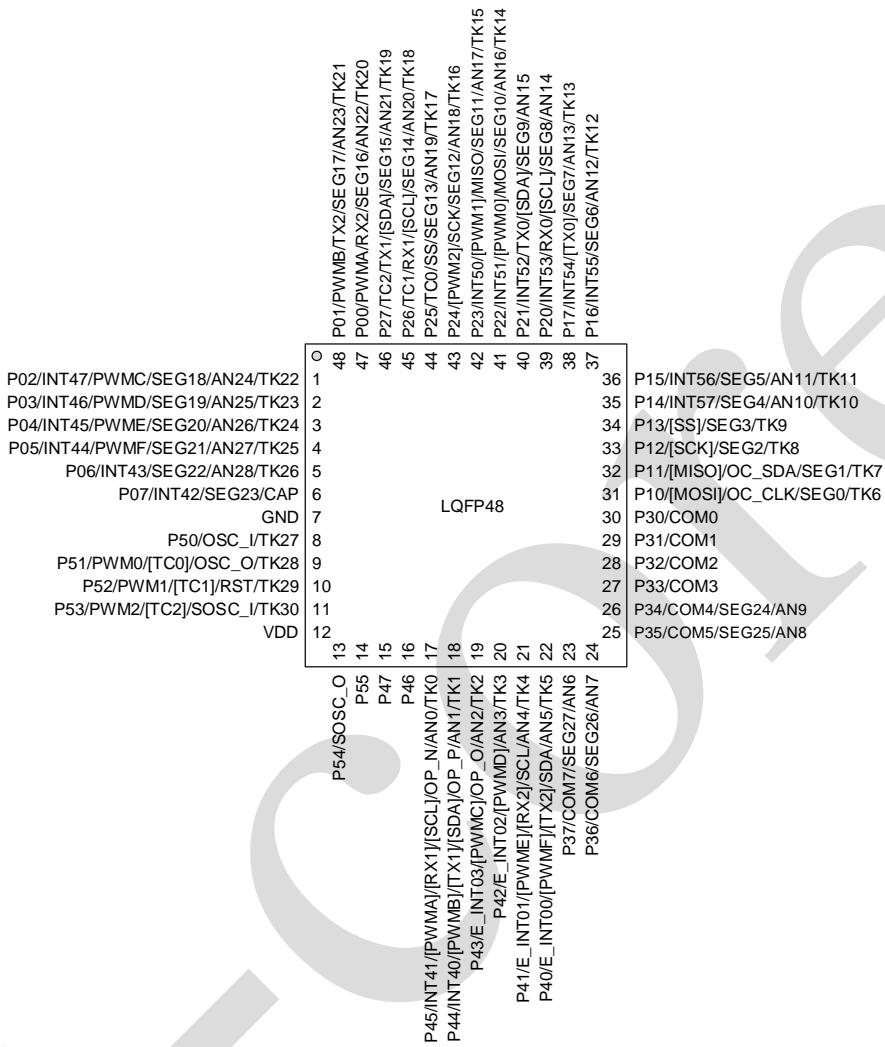

## 2.2 引脚排列图

图 2.2.1 LQFP48(AiP8F3264.LA48)引脚排列图

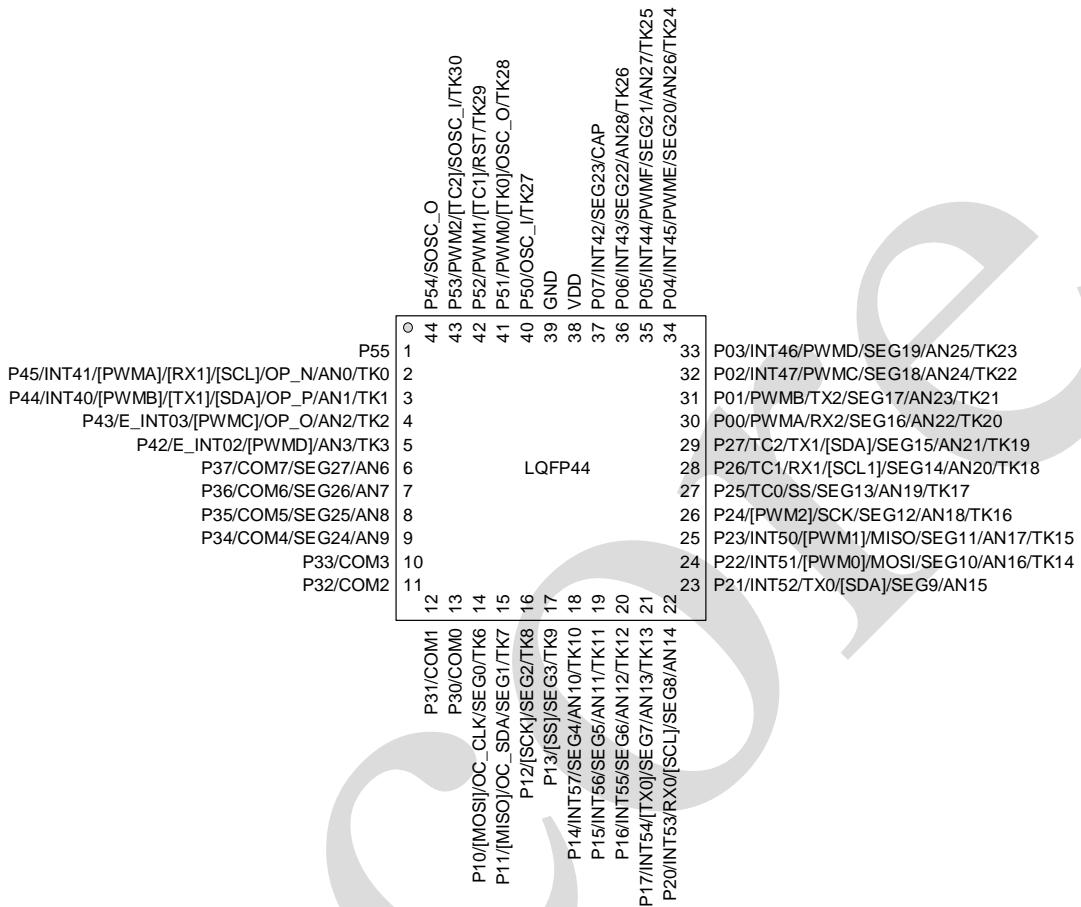

图 2.2.2 LQFP44(AiP8F3264.LB44)引脚排列图

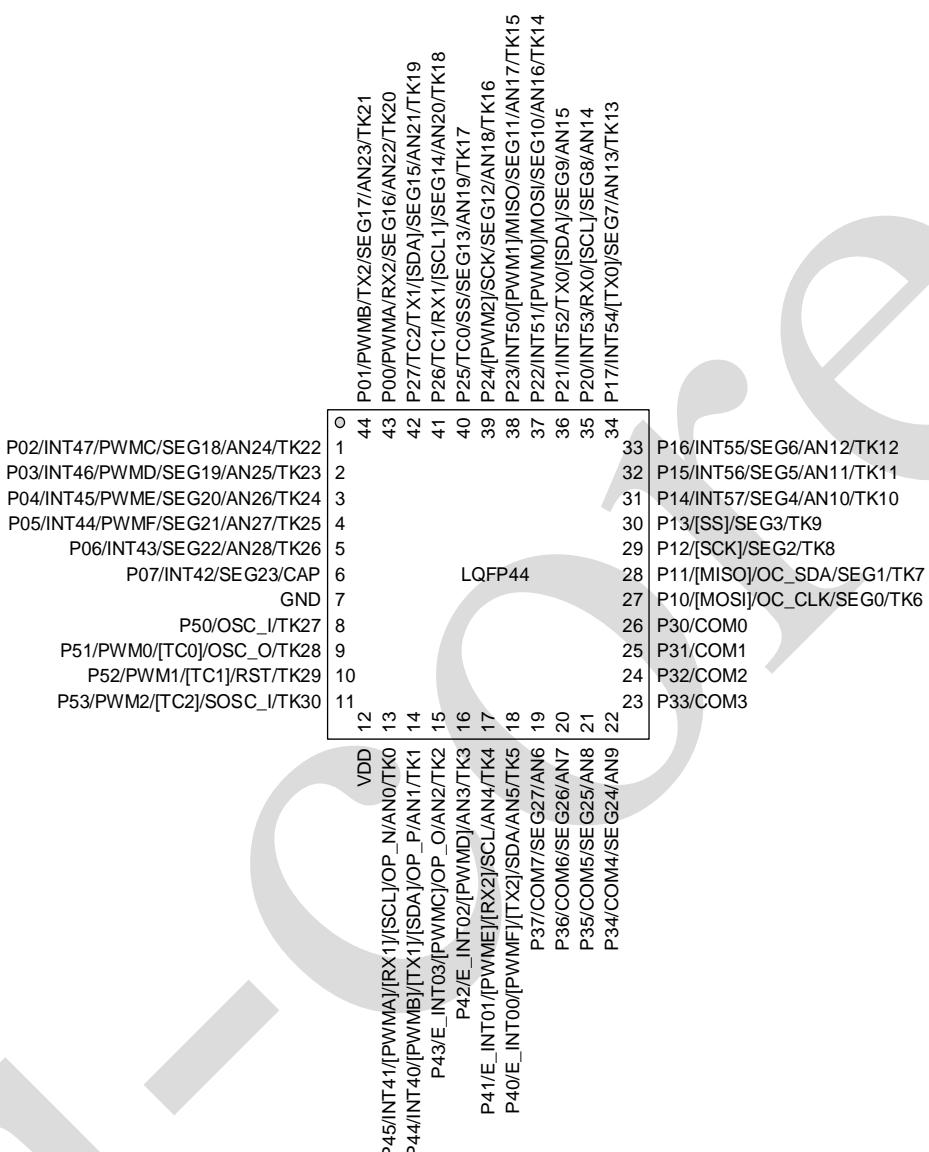

图 2.2.3 LQFP44(AiP8F3264-2.LB44)引脚排列图

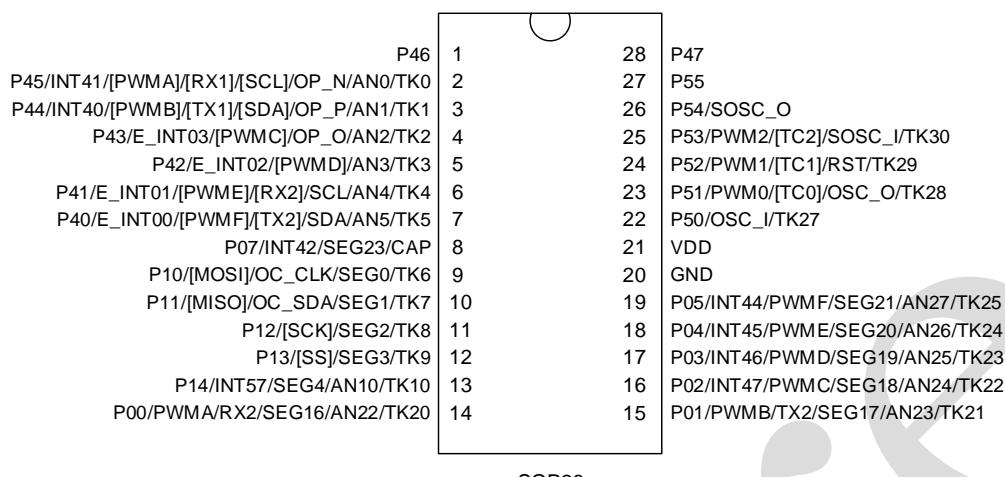

SOP28

图 2.2.4 SOP28(AiP8F3264.SA28)引脚排列图

## 2.3 引脚说明

表 2.3.1 引脚说明

| 引脚名称                                  | 类型  | 说明                       |

|---------------------------------------|-----|--------------------------|

| <b>IO 引脚</b>                          |     |                          |

| P00~P07                               | I/O | 普通 IO 口, 可配置为内部上拉、开漏输出   |

| P10~P17                               | I/O | 普通 IO 口, 可配置为内部上拉、开漏输出   |

| P20~P27                               | I/O | 普通 IO 口, 可配置为内部上拉、开漏输出   |

| P30~P37                               | I/O | 普通 IO 口, 可配置为内部上拉、开漏输出   |

| P40~P47                               | I/O | 普通 IO 口, 可配置为内部上拉、开漏输出   |

| P50~P55                               | I/O | 普通 IO 口, 可配置为内部上拉、开漏输出   |

| <b>定时器引脚</b>                          |     |                          |

| PWM0~PWM2                             | O   | PWM0~2 输出                |

| PWMA、PWMB、<br>PWMC、PWMD、<br>PWME、PWMF | O   | 定时器 5PWM 输出              |

| TC0~TC2                               | I/O | 定时器 0~定时器 2 输入           |

| <b>通讯引脚</b>                           |     |                          |

| TXD0~TXD2                             | O   | UART0、UART1、UART2 数据输出引脚 |

| RXD0~RXD2                             | I   | UART0、UART1、UART2 数据输入引脚 |

| SCL                                   | I/O | I2C 时钟输入/输出引脚            |

| SDA                                   | I/O | I2C 数据通讯引脚               |

| SCK                                   | I/O | 串行时钟输入/输出引脚              |

| MISO                                  | I/O | SPI 主设备输入/从设备输出引脚        |

| MOSI                                  | I/O | SPI 主设备输出/从设备输入引脚        |

无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

表 835-11-B4

编号: AiP8F3264-AX-J001

|                     |     |            |

|---------------------|-----|------------|

| SS                  | I/O | SPI 从动选择输入 |

| <b>ADC 引脚</b>       |     |            |

| AN0~AN28            | I   | AD 输入引脚    |

| <b>TOUCH 引脚</b>     |     |            |

| TK0~TK30            | I   | 触摸按键       |

| CAP                 | I/O | 触摸电容接口     |

| <b>运放&amp;比较器引脚</b> |     |            |

| OP_N                | I   | 运放负端       |

| OP_P                | I   | 运放正端       |

| OP_O                | O   | 运放输出端      |

| <b>特殊引脚</b>         |     |            |

| E_INT0~E_INT3       | I   | 外部中断输入     |

| INT40~INT47         | I   | 外部中断输入     |

| INT50~INT57         | I   | 外部中断输入     |

| COM0~COM7           | O   | LCD 共用信号输出 |

| SEG0~SEG27          | O   | LCD 段选信号输出 |

| OSC_I、OSC_O         | I/O | 主时钟振荡器引脚   |

| SOSC_I、SOSC_O       | I/O | 副时钟振荡器引脚   |

| RST                 | I   | 外部复位引脚     |

| VDD                 | P   | 电源脚        |

| GND                 | G   | 地线         |

| <b>仿真、烧录接口</b>      |     |            |

| OC_SDA              | I/O | 仿真、烧录接口    |

| OC_CLK              | I/O | 仿真、烧录接口    |

### 3 电气特性

#### 3.1 极限参数

表 3.1.1 极限参数

| 符号               | 参数名称     | 最小      | 最大      | 单位 |

|------------------|----------|---------|---------|----|

| VDD              | 供电电压     | GND-0.3 | +6.0    | V  |

| V <sub>IN</sub>  | 输入电压     | GND-0.3 | VDD+0.3 | V  |

| V <sub>OUT</sub> | 输出电压     | GND-0.3 | VDD+0.3 | V  |

| I <sub>VDD</sub> | VDD 最大电流 | —       | -150    | mA |

| I <sub>VSS</sub> | GND 最大电流 | —       | 100     | mA |

| T <sub>A</sub>   | 工作温度     | -40     | +105    | °C |

| T <sub>STG</sub> | 储存温度     | -60     | +150    | °C |

| T <sub>L</sub>   | 焊接温度     | 260     |         | °C |

注: 这是一个额定值, 如果对芯片的操作超过极限参数所规定的范围, 将对芯片造成损坏。

#### 3.2 工作电压-频率

表 3.2.1 工作频率电压特性 (T<sub>A</sub>=25°C, 除非另有说明)

| 符号  | 参数名称 | 条件                                                          | 最小  | 典型 | 最大  | 单位 |

|-----|------|-------------------------------------------------------------|-----|----|-----|----|

| VDD | 工作电压 | f <sub>SYS</sub> =32.768kHz<br>T <sub>A</sub> =25°C         | 1.8 | —  | 5.5 | V  |

|     |      | f <sub>SYS</sub> =4MHz<br>T <sub>A</sub> =25°C              | 1.8 | —  | 5.5 |    |

|     |      | f <sub>SYS</sub> =16MHz<br>T <sub>A</sub> =25°C             | 2.0 | —  | 5.5 |    |

|     |      | f <sub>SYS</sub> =8MHz<br>T <sub>A</sub> =-40°C<br>~+105°C  | 1.8 | —  | 5.5 |    |

|     |      | f <sub>SYS</sub> =16MHz<br>T <sub>A</sub> =-40°C<br>~+105°C | 1.8 | —  | 5.5 |    |

### 3.3 DC 特性

表 3.3.1 DC 特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号                              | 参数名称   | 测试条件                        |                                                    | 最小     | 典型   | 最大     | 单位 |  |

|---------------------------------|--------|-----------------------------|----------------------------------------------------|--------|------|--------|----|--|

| IDD1<br>(RUN)                   | VDD=5V | f <sub>SYS</sub> =16MHz     | —                                                  | 3.0    | 10.0 |        | mA |  |

|                                 | VDD=3V |                             | —                                                  | 3.0    | 10.0 |        |    |  |

|                                 | VDD=5V | f <sub>SYS</sub> =8MHz      | —                                                  | 2.0    | 7.0  |        |    |  |

|                                 | VDD=3V |                             | —                                                  | 2.0    | 7.0  |        |    |  |

| IDD2<br>(RUN)                   | VDD=5V | f <sub>SYS</sub> =32.768kHz | —                                                  | 180    | 400  |        | μA |  |

|                                 | VDD=3V |                             | —                                                  | 180    | 400  |        |    |  |

| IDD3<br>(IDLE)                  | VDD=5V | f <sub>SYS</sub> =16MHz     | —                                                  | 4.5    | 13   |        | mA |  |

|                                 | VDD=3V |                             | —                                                  | 3.5    | 11   |        |    |  |

| IDD4<br>(IDLE)                  | VDD=5V | f <sub>SYS</sub> =32.768kHz | —                                                  | 175    | 400  |        | μA |  |

|                                 | VDD=3V |                             | —                                                  | 175    | 400  |        |    |  |

| I <sub>STB2</sub><br>(STOP<br>) | VDD=5V | WDT 关闭,<br>LVR 关闭。          | —                                                  | 5      | 10   |        | μA |  |

|                                 | VDD=3V |                             | —                                                  | 5      | 10   |        |    |  |

| V <sub>IH</sub>                 | 输入高电平  | IO                          |                                                    | 0.7VDD | —    | VDD    | V  |  |

| V <sub>IL</sub>                 | 输入低电平  | IO                          |                                                    | 0      | —    | 0.3VDD | V  |  |

| I <sub>OH</sub>                 | 输出高电流  | VDD=5V                      | V <sub>OH</sub> =0.9VDD                            | —      | 10   | 20     | mA |  |

|                                 |        | VDD=3V                      |                                                    | —      | 5    | 10     |    |  |

| I <sub>OL1</sub>                | 输出低电流  | VDD=5V                      | V <sub>OL1</sub> =0.1V <sub>DD</sub> ,<br>所有 IO。   | —      | 30   | 60     | mA |  |

|                                 |        | VDD=3V                      |                                                    | —      | 12   | 24     |    |  |

| I <sub>OL2</sub>                | 输出低电流  | VDD=5V                      | V <sub>OL2</sub> =0.1V <sub>DD</sub> ,<br>P3 口大驱动。 | —      | 80   | 120    | mA |  |

|                                 |        | VDD=3V                      |                                                    | —      | 35   | 70     |    |  |

| R <sub>PU</sub>                 | 上拉电阻   | VDD=5V                      | 所有输入管脚                                             | —      | 30   | 60     | kΩ |  |

|                                 |        | VDD=3V                      |                                                    | —      | 30   | 60     |    |  |

| I <sub>IH</sub>                 | 输入高漏电流 | VDD=5V, 所有输入管脚              |                                                    | —      | —    | 1      | μA |  |

| I <sub>IL</sub>                 | 输入低漏电流 | VDD=5V, 所有输入管脚              |                                                    | -1     | —    | —      | μA |  |

### 3.4 上电复位特性

表 3.4.1 上电复位特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号               | 参数名称     | 测试条件 |   | 最小   | 典型  | 最大  | 单位   |

|------------------|----------|------|---|------|-----|-----|------|

| V <sub>POR</sub> | 复位电平     | —    | — | —    | 1.4 | —   | V    |

| t <sub>R</sub>   | VDD 上升时间 | —    | — | 0.05 | —   | 0.5 | V/ms |

### 3.5 LVR&LVD 电气特性

表 3.5.1 LVR&LVD 电气特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号               | 参数名称 | 测试条件 | 最小 | 典型   | 最大  | 单位 |

|------------------|------|------|----|------|-----|----|

| V <sub>LVR</sub> | 低压复位 | —    | —  | 1.90 | —   | V  |

|                  |      |      | —  | 2.00 | —   |    |

|                  |      |      | —  | 2.10 | —   |    |

|                  |      |      | —  | 2.20 | —   |    |

|                  |      |      | —  | 2.32 | —   |    |

|                  |      |      | —  | 2.44 | —   |    |

|                  |      |      | —  | 2.59 | —   |    |

|                  |      |      | —  | 2.75 | —   |    |

|                  |      |      | —  | 2.93 | —   |    |

|                  |      |      | —  | 3.14 | —   |    |

|                  |      |      | —  | 3.38 | —   |    |

|                  |      |      | —  | 3.67 | —   |    |

| V <sub>LVD</sub> | 低压检测 | —    | —  | 2.00 | —   | V  |

|                  |      |      | —  | 2.10 | —   |    |

|                  |      |      | —  | 2.20 | —   |    |

|                  |      |      | —  | 2.32 | —   |    |

|                  |      |      | —  | 2.44 | —   |    |

|                  |      |      | —  | 2.59 | —   |    |

|                  |      |      | —  | 2.75 | —   |    |

|                  |      |      | —  | 2.93 | —   |    |

|                  |      |      | —  | 3.14 | —   |    |

|                  |      |      | —  | 3.38 | —   |    |

|                  |      |      | —  | 3.67 | —   |    |

|                  |      |      | —  | 4.00 | —   |    |

| ΔV               | 迟滞电压 | —    | —  | 0.1  | 0.2 | V  |

### 3.6 内部高速 RC 振荡器特性

表 3.6.1 内部高速 RC 振荡器特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号         | 参数名称            | 测试条件                                                      | 最小   | 典型 | 最大   | 单位  |

|------------|-----------------|-----------------------------------------------------------|------|----|------|-----|

| $f_{HIRC}$ | 内部高速振荡频率 (HIRC) | VDD=2.0V~5.5V                                             | —    | 16 | —    | MHz |

| —          | 频率-温度特性         | VDD=5.0V, $T_A=0^\circ\text{C} \sim +50^\circ\text{C}$    | -1.5 | —  | +1.5 | %   |

|            |                 | VDD=5.0V, $T_A=-20^\circ\text{C} \sim +70^\circ\text{C}$  | -2   | —  | +2   |     |

|            |                 | VDD=5.0V, $T_A=-40^\circ\text{C} \sim +105^\circ\text{C}$ | -2.5 | —  | +2.5 |     |

### 3.7 内部低速 RC 振荡器特性

表 3.7.1 内部低速 RC 振荡器特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号         | 参数名称            | 测试条件                                                      | 最小 | 典型 | 最大 | 单位  |

|------------|-----------------|-----------------------------------------------------------|----|----|----|-----|

| $f_{LIRC}$ | 内部低速振荡频率 (LIRC) | VDD=5.0V                                                  | —  | 16 | —  | kHz |

| —          | 频率-温度特性         | VDD=5.0V, $T_A=-40^\circ\text{C} \sim +105^\circ\text{C}$ | -5 | —  | +5 | %   |

### 3.8 ADC 电气特性

表 3.8.1 ADC 电气特性 (VDD=5V,  $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号          | 参数名称       | 测试条件                                                      | 最小  | 典型      | 最大        | 单位       |

|-------------|------------|-----------------------------------------------------------|-----|---------|-----------|----------|

| $V_{AD}$    | ADC 工作电压   | —                                                         | 2.0 | —       | 5.5       | V        |

| INL         | 积分非线性误差    | $V_{REF}=VDD$                                             | —   | $\pm 8$ | $\pm 16$  | LSB      |

| DNL         | 微分非线性误差    | $V_{REF}=VDD$                                             | —   | $\pm 6$ | $\pm 10$  |          |

| $V_{AIN}$   | 输入电压       | —                                                         | 0   | —       | $V_{REF}$ | V        |

| $Z_{AIN}$   | 输入阻抗       | —                                                         | —   | —       | 10        | kΩ       |

| $T_{cycle}$ | ADC 时钟周期   | —                                                         | 125 | —       | —         | ns       |

| $T_{AD}$    | ADC 转换周期   | —                                                         | —   | 12      | —         | $T_{AD}$ |

| $V_{REF1}$  | 内部 2V 参考电压 | $VDD=5.0V, T_A=-40^\circ\text{C} \sim +105^\circ\text{C}$ | —   | 2       | —         | V        |

| $V_{REF2}$  | 内部 3V 参考电压 | $VDD=5.0V, T_A=-40^\circ\text{C} \sim +105^\circ\text{C}$ | —   | 3       | —         | V        |

| $V_{REF3}$  | 内部 4V 参考电压 | $VDD=5.0V, T_A=-40^\circ\text{C} \sim +105^\circ\text{C}$ | —   | 4       | —         | V        |

### 3.9 OPA 电气特性

表 3.9.1 OPA 特性 (VDD=5V, TA=25°C, 除非另有说明)

| 符号              | 参数名称   | 测试条件      | 最小  | 典型  | 最大      | 单位   |

|-----------------|--------|-----------|-----|-----|---------|------|

| VDD             | 工作电压   | —         | 2   | —   | 5.5     | V    |

| I <sub>DD</sub> | 静态电流   | VDD=5V    | —   | 500 | —       | μA   |

| V <sub>OS</sub> | 输入失调   | —         | -2  | —   | 2       | mV   |

| V <sub>CM</sub> | 共模电压范围 | CMRR>50dB | —   | —   | VDD-1.4 | V    |

| PSRR            | 电源抑制比  | —         | 60  | 80  | —       | dB   |

| CMRR            | 共模抑制比  | —         | 60  | 80  | —       | dB   |

| Loop-Gain       | 开环增益   | —         | —   | 80  | —       | dB   |

| SR+             | 正摆率    | —         | 0.6 | 1.8 | —       | V/μs |

| SR-             | 负摆率    | —         | 0.6 | 1.8 | —       | V/μs |

| GBW             | 增益带宽   | —         | 0.6 | 2   | —       | MHz  |

### 3.10 CMP 电气特性

表 3.10.1 CMP 特性 (VDD=5V, TA=25°C, 除非另有说明)

| 符号               | 参数名称    | 测试条件                       | 最小 | 典型   | 最大 | 单位 |

|------------------|---------|----------------------------|----|------|----|----|

| I <sub>DD</sub>  | 静态电流    | VDD=5V                     | —  | 500  | —  | μA |

| V <sub>OS</sub>  | 输入失调    | —                          | -2 | —    | 2  | mV |

| V <sub>HYS</sub> | 迟滞电压    | —                          | —  | 40   | —  | mV |

| T <sub>S</sub>   | 小信号响应时间 | VN=1.2V,<br>VP=1.15V~1.25V | —  | 2.26 | —  | μs |

| T <sub>L</sub>   | 大信号响应时间 | VN=1V, VP=0V~2V            | —  | 0.83 | —  | μs |

### 3.11 LCD 电气特性

表 3.11.1 LCD 电压特性 (VDD=5V, TA=25°C, 除非另有说明)

| 符号               | 参数名称   | 测试条件                                                                                                                                                            | 最小 | 典型                                                                                                                                           | 最大 | 单位 |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------|----|----|

| V <sub>LCD</sub> | LCD 电压 | 无负载<br>LCDRH=00H<br>LCDRH=01H<br>LCDRH=02H<br>LCDRH=03H<br>LCDRH=04H<br>LCDRH=05H<br>LCDRH=06H<br>LCDRH=07H<br>LCDRH=08H<br>LCDRH=09H<br>LCDRH=0AH<br>LCDRH=0BH | —  | 0.531VDD<br>0.563VDD<br>0.594VDD<br>0.625VDD<br>0.656VDD<br>0.688VDD<br>0.719VDD<br>0.750VDD<br>0.781VDD<br>0.813VDD<br>0.844VDD<br>0.875VDD | —  | V  |

无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

表 835-11-B4

编号: AiP8F3264-AX-J001

|  |  |  |            |  |          |  |  |

|--|--|--|------------|--|----------|--|--|

|  |  |  | LCDCRH=0CH |  | 0.906VDD |  |  |

|  |  |  | LCDCRH=0DH |  | 0.938VDD |  |  |

|  |  |  | LCDCRH=0EH |  | 0.969VDD |  |  |

|  |  |  | LCDCRH=0FH |  | 1.000VDD |  |  |

### 3.12 LXT 电气特性

表 3.12.1 LXT 振荡特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号        | 参数名称           | 测试条件     | 最小 | 典型     | 最大 | 单位  |

|-----------|----------------|----------|----|--------|----|-----|

| $f_{LXT}$ | 外部低速振荡频率 (LXT) | VDD=5.0V | —  | 32.768 | —  | kHz |

| $C_L$     | 匹配电容           | VDD=5.0V | —  | 22     | —  | pF  |

### 3.13 AC 特性参数

表 3.13.1 AC 特性 ( $T_A=25^\circ\text{C}$ , 除非另有说明)

| 符号          | 参数名称     | 测试条件   | 最小 | 典型 | 最大 | 单位 |

|-------------|----------|--------|----|----|----|----|

| $t_{RESET}$ | 外部复位最小脉宽 | VDD=5V | 10 | —  | —  | μs |

| $t_{INT}$   | 外部中断最小脉宽 | VDD=5V | 10 | —  | —  | μs |

### 3.14 Flash 存储器参数

表 3.14.1 Flash 存储器特性

| 符号        | 参数名称       | 测试条件                             | 最小   | 典型 | 最大  | 单位  |

|-----------|------------|----------------------------------|------|----|-----|-----|

| $T_{FER}$ | Flash 擦除时间 | VDD=5V, $T_a=25^\circ\text{C}$ 。 | —    | —  | 2   | ms  |

| $T_{FWR}$ | Flash 写时间  | VDD=5V, $T_a=25^\circ\text{C}$ 。 | —    | —  | 200 | us  |

| EP        | Flash 擦写次数 | —                                | 100K | —  | —   | E/W |

## 4 存储器

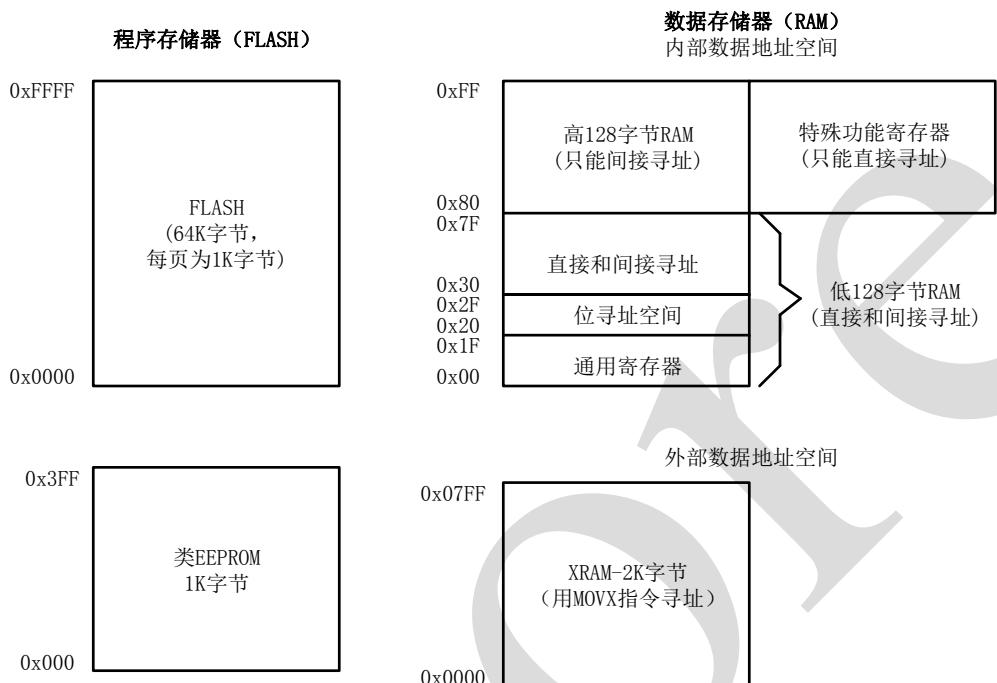

AiP8F3264 有两个独立的存储器空间, 程序存储器和数据存储器, 下图所示是存储器组织结构图。

### 4.1 IAP 寄存器列表

表 4.1.1 FLASH 寄存器列表

| 寄存器名称 | 地址  | 描述            | 初值  |

|-------|-----|---------------|-----|

| FSCR  | FCH | Flash 控制寄存器   | 00H |

| FSDR  | FDH | Flash 数据寄存器   | 00H |

| FSALR | FEH | Flash 地址低位寄存器 | 00H |

| FSAHR | FFH | Flash 地址高位寄存器 | 00H |

| FSCR1 | DEH | Flash 页保护寄存器  | 00H |

## 4.2 IAP 寄存器说明

表 4.2.1 FSCR 寄存器

| Bit  | 7   | 6   | 5     | 4     | 3     | 2     | 1         | 0         |

|------|-----|-----|-------|-------|-------|-------|-----------|-----------|

| Name | —   | —   | EE_EN | EE_WR | EE_RD | EE_ER | INS_ER_EH | INS_WR_EH |

| R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   | R/W       | R/W       |

| POR  | 0   | 0   | 0     | 0     | 0     | 0     | 0         | 0         |

| 位 | 字段        | 描述                                                                                                                                   |

|---|-----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 5 | EE_EN     | EEPROM 使能位<br>EE 使能位, 向 EE 操作前需将此位置高。将此位清零时, 禁止向 EE 操作。配置完 EE_WR/EE_RD/EE_ER 位后, 使能 EE_EN 位。<br>当 EE 操作结束后硬件自动清零。<br>1: 使能<br>0: 不使能 |

| 4 | EE_WR     | EE 写控制位<br>此位为 EE 写控制位, 由软件置 1, 激活写周期。<br>写周期结束后硬件自动清零。当 EE_EN 未先置高时, 此位置高无效。<br>1: 写周期有效<br>0: 写周期结束                                |

| 3 | EE_RD     | EE 读控制位<br>此位为 EE 读控制位, 由软件置 1, 激活读周期。<br>读周期结束后硬件自动清零。当 EE_EN 未先置高时, 此位置高无效。<br>1: 读周期有效<br>0: 读周期结束                                |

| 2 | EE_ER     | EE 擦控制位<br>此位为 EE 擦控制位, 由软件置 1, 激活读周期。<br>擦周期结束后硬件自动清零。当 EE_EN 未先置高时, 此位置高无效。<br>1: 擦周期有效<br>0: 擦周期结束                                |

| 1 | INS_ER_EH | 自编程页擦除使能<br>置 1 时将启动一个页擦除周期, 擦除完成后将由硬件自动清零                                                                                           |

| 0 | INS_WR_EH | 自编程单字节写使能<br>置 1 时将启动一个写周期, 编程完成后将由硬件自动清零                                                                                            |

注: 位 1 和位 0 不能同时置 1, 读取位 1 和位 0 总是返回 0。

表 4.2.2 FSDR 寄存器

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name |     |     |     |     |     |     |     |     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 字段   | 描述                   |

|-----|------|----------------------|

| 7-0 | FSDR | 程序存储器数据位 bit 7~bit 0 |

表 4.2.3 FSALR 寄存器

| Bit  | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-------|-----|-----|-----|-----|-----|-----|-----|

| Name | FSALR |     |     |     |     |     |     |     |

| R/W  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 字段    | 描述                        |

|-----|-------|---------------------------|

| 7-0 | FSALR | Flash 程序存储器地址 bit 7~bit 0 |

表 4.2.4 FSAHR 寄存器

| Bit  | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-------|-----|-----|-----|-----|-----|-----|-----|

| Name | FSAHR |     |     |     |     |     |     |     |

| R/W  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 字段    | 描述                         |

|-----|-------|----------------------------|

| 7-0 | FSAHR | Flash 程序存储器地址 bit 15~bit 8 |

表 4.2.5 FSCR1 寄存器

| Bit  | 7   | 6   | 5           | 4   | 3   | 2   | 1   | 0   |  |  |

|------|-----|-----|-------------|-----|-----|-----|-----|-----|--|--|

| Name | -   | -   | FLASH_LEVEL |     |     |     |     |     |  |  |

| R/W  | R/W | R/W | R/W         | R/W | R/W | R/W | R/W | R/W |  |  |

| POR  | 0   | 0   | 0           | 0   | 0   | 0   | 0   | 0   |  |  |

| 位           | 字段                   | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

|-------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|--------|------|--------|---------------------|--------|---------------------|--------|---------------------|--------|---------------------|--------|---------------------|--------|----------------------|--------|----------------------|--------|---------------------|--------|---------------------|--------|----------------------|--------|----------------------|

| 5-0         | FLASH_LEVEL          | 自编程页保护设置<br><table border="1"><tr><td>FLASH_LEVEL</td><td>被保护页</td></tr><tr><td>000000</td><td>无页保护</td></tr><tr><td>000001</td><td>地址 0x0000~0x07FF 保护</td></tr><tr><td>000010</td><td>地址 0x0000~0xBFFF 保护</td></tr><tr><td>000011</td><td>地址 0x0000~0xFFFF 保护</td></tr><tr><td>000100</td><td>地址 0x0000~0x13FF 保护</td></tr><tr><td>000101</td><td>地址 0x0000~0x17FF 保护</td></tr><tr><td>000110</td><td>地址 0x0000~0x1BFFF 保护</td></tr><tr><td>000111</td><td>地址 0x0000~0x1FFFF 保护</td></tr><tr><td>001000</td><td>地址 0x0000~0x23FF 保护</td></tr><tr><td>001001</td><td>地址 0x0000~0x27FF 保护</td></tr><tr><td>001010</td><td>地址 0x0000~0x2BFFF 保护</td></tr><tr><td>001011</td><td>地址 0x0000~0x2FFFF 保护</td></tr></table> | FLASH_LEVEL | 被保护页 | 000000 | 无页保护 | 000001 | 地址 0x0000~0x07FF 保护 | 000010 | 地址 0x0000~0xBFFF 保护 | 000011 | 地址 0x0000~0xFFFF 保护 | 000100 | 地址 0x0000~0x13FF 保护 | 000101 | 地址 0x0000~0x17FF 保护 | 000110 | 地址 0x0000~0x1BFFF 保护 | 000111 | 地址 0x0000~0x1FFFF 保护 | 001000 | 地址 0x0000~0x23FF 保护 | 001001 | 地址 0x0000~0x27FF 保护 | 001010 | 地址 0x0000~0x2BFFF 保护 | 001011 | 地址 0x0000~0x2FFFF 保护 |

| FLASH_LEVEL | 被保护页                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000000      | 无页保护                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000001      | 地址 0x0000~0x07FF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000010      | 地址 0x0000~0xBFFF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000011      | 地址 0x0000~0xFFFF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000100      | 地址 0x0000~0x13FF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000101      | 地址 0x0000~0x17FF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000110      | 地址 0x0000~0x1BFFF 保护 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 000111      | 地址 0x0000~0x1FFFF 保护 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 001000      | 地址 0x0000~0x23FF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 001001      | 地址 0x0000~0x27FF 保护  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 001010      | 地址 0x0000~0x2BFFF 保护 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

| 001011      | 地址 0x0000~0x2FFFF 保护 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |      |        |      |        |                     |        |                     |        |                     |        |                     |        |                     |        |                      |        |                      |        |                     |        |                     |        |                      |        |                      |

# 无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

表 835-11-B4

编号: AiP8F3264-AX-J001

|        |                     |

|--------|---------------------|

| 001100 | 地址 0x0000~0x33FF 保护 |

| 001101 | 地址 0x0000~0x37FF 保护 |

| 001110 | 地址 0x0000~0x3BFF 保护 |

| 001111 | 地址 0x0000~0x3FFF 保护 |

| 010000 | 地址 0x0000~0x43FF 保护 |

| 010001 | 地址 0x0000~0x47FF 保护 |

| 010010 | 地址 0x0000~0x4BFF 保护 |

| 010011 | 地址 0x0000~0x4FFF 保护 |

| 010100 | 地址 0x0000~0x53FF 保护 |

| 010101 | 地址 0x0000~0x57FF 保护 |

| 010110 | 地址 0x0000~0x5BFF 保护 |

| 010111 | 地址 0x0000~0x5FFF 保护 |

| 011000 | 地址 0x0000~0x63FF 保护 |

| 011001 | 地址 0x0000~0x67FF 保护 |

| 011010 | 地址 0x0000~0x6BFF 保护 |

| 011011 | 地址 0x0000~0x6FFF 保护 |

| 011100 | 地址 0x0000~0x73FF 保护 |

| 011101 | 地址 0x0000~0x77FF 保护 |

| 011110 | 地址 0x0000~0x7BFF 保护 |

| 011111 | 地址 0x0000~0x7FFF 保护 |

| 100000 | 地址 0x0000~0x83FF 保护 |

| 100001 | 地址 0x0000~0x87FF 保护 |

| 100010 | 地址 0x0000~0x8BFF 保护 |

| 100011 | 地址 0x0000~0x8FFF 保护 |

| 100100 | 地址 0x0000~0x93FF 保护 |

| 100101 | 地址 0x0000~0x97FF 保护 |

| 100110 | 地址 0x0000~0x9BFF 保护 |

| 100111 | 地址 0x0000~0x9FFF 保护 |

| 101000 | 地址 0x0000~0xA3FF 保护 |

| 101001 | 地址 0x0000~0xA7FF 保护 |

| 101010 | 地址 0x0000~0xABFF 保护 |

| 101011 | 地址 0x0000~0xAFFF 保护 |

| 101100 | 地址 0x0000~0xB3FF 保护 |

| 101101 | 地址 0x0000~0xB7FF 保护 |

| 101110 | 地址 0x0000~0xBBFF 保护 |

| 101111 | 地址 0x0000~0xBFFF 保护 |

| 110000 | 地址 0x0000~0xC3FF 保护 |

| 110001 | 地址 0x0000~0xC7FF 保护 |

| 110010 | 地址 0x0000~0xCBFF 保护 |

| 110011 | 地址 0x0000~0xCFFF 保护 |

|  |  |        |                     |

|--|--|--------|---------------------|

|  |  | 110100 | 地址 0x0000~0xD3FF 保护 |

|  |  | 110101 | 地址 0x0000~0xD7FF 保护 |

|  |  | 110110 | 地址 0x0000~0xDBFF 保护 |

|  |  | 110111 | 地址 0x0000~0xDFFF 保护 |

|  |  | 111000 | 地址 0x0000~0xE3FF 保护 |

|  |  | 111001 | 地址 0x0000~0xE7FF 保护 |

|  |  | 111010 | 地址 0x0000~0xEBFF 保护 |

|  |  | 111011 | 地址 0x0000~0xFFFF 保护 |

|  |  | 111100 | 地址 0x0000~0xF3FF 保护 |

|  |  | 111101 | 地址 0x0000~0xF7FF 保护 |

|  |  | 111110 | 地址 0x0000~0xFBFF 保护 |

|  |  | 111111 | 地址 0x0000~0xFFFF 保护 |

### 4.3 程序存储器

程序存储器包含 64KB FLASH ROM，可用来存放用户程序，以 1KB 为 1 个扇区，可以在系统编程。一个 FLASH 位一旦被清“0”，必须经过擦除才能再回到“1”状态。在进行重新编程之前，一般要将数据字节擦除（置为 0xFF）。为了保证操作正确，写和擦除操作由硬件自动完成，不需要进行数据查询来判断写/擦除操作何时结束。在 FLASH 写/擦除操作期间，程序暂停执行。

#### 4.3.1FLASH 页擦除

写 FLASH 存储器可以清除数据位，但不能使数据位置“1”，只有擦除操作能将 FLASH 中的数据位置“1”。所以在写入新值之前，必须先擦除待编程的地址。FLASH 存储器共 64 页（每页 1K 字节），一次擦除操作将擦除一页（将页内的所有字节置为 0xFF）。

页擦除的步骤如下：

1. 配置 FLASH 写入地址寄存器 FSAHR/FSALR（待擦除的页任意一个地址均可）

2. 配置 FLASH 写入数据寄存器 FSADR（写入数据建议配置为 0x00）

3. 对 KEYCODE 寄存器依次写入 0x3C、0x02、0xA1 关闭 FSCR 寄存器写保护

4. 使能擦除操作，NOP，NOP，NOP

5. 对 KEYCODE 寄存器写入 0x00 打开 FSCR 寄存器写保护

例如擦除 0AA0H 地址对应的扇区，则可执行下述程序：

```

MOV      FSAHR, #0AH

MOV      FSALR, #0A0H

MOV      FSADR, #00H

```

---

|     |                |

|-----|----------------|

| MOV | KEYCODE, #3CH  |

| MOV | KEYCODE, #02H  |

| MOV | KEYCODE, #0A1H |

| MOV | FSCR, #02H     |

| NOP |                |

| NOP |                |

| NOP |                |

| MOV | KEYCODE, #00H  |

#### 4.3.2FLASH 编程

FLASH 存储器一次只能写入一个字节。

用软件对 FLASH 字节编程的步骤如下:

1. 配置 FLASH 写入地址寄存器 FSAHR/FSALR (目标地址)

2. 配置 FLASH 写入数据寄存器 FSDR (目标地址对应的数据)

3. 对 KEYCODE 寄存器依次写入 0x3C、0x02、0xA1 关闭 FSCR 寄存器写保护

4. 使能写操作, NOP, NOP, NOP

5. 对 KEYCODE 寄存器写入 0x00 打开 FSCR 寄存器写保护

例如要向 0AA0H 地址写入一个数据 0x55, 则可执行下述程序:

|     |                |

|-----|----------------|

| MOV | FSAHR, #0AH    |

| MOV | FSALR, #0A0H   |

| MOV | FSDR, #55H     |

| MOV | KEYCODE, #3CH  |

| MOV | KEYCODE, #02H  |

| MOV | KEYCODE, #0A1H |

| MOV | FSCR, #01H     |

| NOP |                |

| NOP |                |

| NOP |                |

| MOV | KEYCODE, #00H  |

### 4.3.3FLASH 读取

FLASH 存储器可以一次读一个字节，读操作通过 MOVC 指令实现。

例如读取 0x0300H 地址的数据，则可执行下述程序：

```

#include <absacc.h>

KEYCODE = 0x3C;

KEYCODE = 0x02;

KEYCODE = 0xA1;

dat = CBYTE[0x0300];

KEYCODE = 0x00;

```

### 4.4 数据存储器

AiP8F3264 的数据存储器空间中有 256B 的内部 RAM，位于 0x00 到 0xFF 的地址空间。

数据存储器中的低 128B 为通用寄存器，可以用直接或间接寻址方式访问。其中 0x00 到 0x1F 为 4 个通用寄存器区，每个区有 8 个 8 位寄存器；地址 0x20 到 0x2F，既可以按字节寻址又可以作为 128 个位地址用直接位寻址方式访问。

数据存储器中的高 128B 只能用间接寻址访问，该存储区与特殊功能寄存器（SFR）占据相同的地址空间，但物理上与 SFR 空间分开。当使用直接寻址方式的指令访问高于 0x7F 的地址时，将访问 SFR 空间；当使用间接寻址方式的指令访问高于 0x7F 的地址时，将访问数据存储器的高 128 字节。

#### 4.4.1 通用寄存器

从地址 0x00 到 0x1F，可以作为 4 个通用寄存器区访问，每个区有 8 个 8 位寄存器，称为 R0-R7。在同一时刻只能选择一个寄存器区，程序状态字中的 RS0(PSW.3) 和 RS1(PSW.4) 位用于选择当前的寄存器区，间接寻址方式使用 R0 和 R1 作为间址寄存器。

#### 4.4.2 位寻址空间

从地址 0x20 到 0x2F 的 16 个数据存储器单元可以作为 128 个独立寻址位访问。每个位有一个位地址，从 0x00 到 0x7F。位于地址 0x20 的数据字节的 BIT0 位地址为 0x00，位于 0x20 的数据字节的 BIT7 位地址为 0x07，位于 0x2F 的数据字节的 BIT7 位地址为 0x7F。由所用指令的类型来区分是位寻址还是字节寻址。

#### 4.4.3堆栈

程序的堆栈可以位于 256B 数据存储器中的任何位置, 堆栈区域用堆栈指针(SP, 0x81)指定, SP 指向最后使用的位置。下一个压入堆栈的数据将被存放在 SP+1, 然后 SP 加 1, 堆栈深度最大 256 级。

复位后堆栈指针被初始化为地址 0x07, 因此第一个被压入堆栈的数据将被存放在地址 0x08, 这也是寄存器区 1 的第一个寄存器 (R0)。如果使用不止一个寄存器区, SP 应被初始化为数据存储器中不用于数据存储的位置。

#### 4.4.4特殊功能寄存器

从地址 0x80 到 0xFF, 采用直接寻址存储器空间为特殊功能寄存器 (SFR)。通过操作 SFR 对 AiP8F3264 系统和外设的控制及数据交换。用直接寻址方式访问 0x80~0xFF 的存储器空间将访问特殊功能寄存器 (SFR), 地址以 0x0 或 0x8 结尾的 SFR (例如 ACC、IE0、IE1、PSW 等) 既可以按字节寻址也可以按位寻址, 所有其它 SFR 只能按字节寻址。FSCR 寄存器有 KEYCODE 设计, 出于软件安全的考虑, 在将数据写入该 SFR 之前, 必须先按顺序正确地将 KEYCODE 数值写入到 KEYCODE 寄存器中。SFR 空间中未使用的地址保留, 访问这些地址会产生不确定的结果, 应予避免。

下表列出了 AiP8F3264 系统控制器中的全部 SFR, 有关每个寄存器的详细说明请参见各章节寄存器说明。

表 4.4.1 特殊功能寄存器地址映射表

| 高 5 位<br>地址 | 低 3 位地址 |          |                  |                |                     |                    |                     |           |

|-------------|---------|----------|------------------|----------------|---------------------|--------------------|---------------------|-----------|

|             | 0H      | 1H       | 2H               | 3H             | 4H                  | 5H                 | 6H                  | 7H        |

| F8H         | IP1     | CRCIN    | CRCDR            | CRCDRH         | FSCR <sup>注2</sup>  | FSDR               | FSALR               | FSAHR     |

| F0H         | B       | —        | —                | —              | SYSCR <sup>注1</sup> | CKCR <sup>注1</sup> | OSCCR1              | OSCTS     |

| E8H         | RSTFR   | MDAH0    | MDAH1            | MDBH0          | MDBH1               | MDCH0              | MDCH1               | OPACR     |

| E0H         | ACC     | MDAL0    | MDAL1            | MDBL0          | MDBL1               | MDCL0              | MDCL1               | MDUCR     |

| D8H         | LVRCR   | I2CCR1   | SPICR1           | SPICR2         | SPISR               | SPIDR              | FSCR1 <sup>注2</sup> | KEYCODE   |

| D0H         | PSW     | I2CSR1   | I2CSR2           | I2CDR          | I2CADDR             | I2CCCR             | I2CCCRH             | I2CSDHR   |

| C8H         | OSCCR   | UART2CR1 | UART2CR2         | UART2CR3       | UART2DR             | UART2SR            | UART2BRR1           | UART2BRR2 |

| C0H         | EIFLAG0 | UART1CR1 | UART1CR2         | UART1CR3       | UART1SR             | UART1DR            | UART1BRR1           | UART1BRR2 |

| B8H         | IP0     | UART0CR1 | UART0CR2         | UART0CR3       | UART0DR             | UART0SR            | UART0BRR1           | UART0BRR2 |

| B0H         | P3      | T2CR1    | T2CR2            | T2DR1L         | T2DR1H              | T2DR2L             | T2DR2H              | EIFLAG1   |

| A8H         | IE0     | IE1      | IE2              | ADCCRL         | ADCCR               | ADCDRL             | ADCDRH              | P5IO      |

| A0H         | P2      | T1CR1    | T1CR2            | T1DR1L         | T1DR1H              | T1DR2L             | T1DR2H              | P4IO      |

| 98H         | P5      | T0CR1    | T0CR2            | T0DR1L         | T0DR1H              | T0DR2L             | T0DR2H              | P3IO      |

| 90H         | P1      | DPS      | WDTCR            | WTCR           | —                   | P0IO               | P1IO                | P2IO      |

| 88H         | P4      | —        | WDTDR/<br>WDTCNT | WTDR/<br>WTCNT | EIFLAG2             | —                  | FRECR               | FRECNT    |

| 80H         | P0      | SP       | DPL              | DPH            | DPL1                | DPH1               | LVICR               | PCON      |

注:

- 1、需预先写入 KEYCODE 解锁写保护: 3C、02、A0, 写结束后写入 00 打开写保护

2、需预先写入 KEYCODE 解锁写保护: 3C、02、A1, 写结束后写入 00 打开写保护

#### 4.4.5 系统控制寄存器

表 4.4.2 ACC 累加器

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name | ACC |     |     |     |     |     |     |     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 4.4.3 B 寄存器

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name | B   |     |     |     |     |     |     |     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 4.4.4 SP 堆栈指针

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name | SP  |     |     |     |     |     |     |     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |

表 4.4.5 DPL 数据指针寄存器 L

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name | DPL |     |     |     |     |     |     |     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 4.4.6 DPL 数据指针寄存器 H

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name | DPH |     |     |     |     |     |     |     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 4.4.7 DPL1 数据指针寄存器 Low1

| Bit  | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|------|-----|-----|-----|-----|-----|-----|-----|

| Name | DPL1 |     |     |     |     |     |     |     |

| R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 4.4.8 DPH1 数据指针寄存器 High1

| Bit  | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|------|-----|-----|-----|-----|-----|-----|-----|

| Name | DPH1 |     |     |     |     |     |     |     |

| R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

表 4.4.9 PSW 程序状态寄存器

| Bit  | 7   | 6   | 5   | 4        | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|----------|-----|-----|-----|-----|

| Name | CY  | AC  | F0  | RS[1: 0] |     | OV  | F1  | P   |

| R/W  | R/W | R/W | R/W | R/W      | R/W | R/W | R/W | R/W |

| POR  | 0   | 0   | 0   | 0        | 0   | 0   | 0   | 0   |

| 位 | 字段 | 描述        |

|---|----|-----------|

| 7 | CY | 进位标志      |

| 6 | AC | 辅助进位标志    |

| 5 | F0 | 通用用户可定义标志 |

|     |          | 寄存器组选择位                                                                                                                                   |     |     |           |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|

| 4-3 | RS[1: 0] | RS1                                                                                                                                       | RS0 | 寄存器 | 地址        |

|     |          | 0                                                                                                                                         | 0   | 0   | 0x00-0x07 |

|     |          | 0                                                                                                                                         | 1   | 1   | 0x08-0x0F |

|     |          | 1                                                                                                                                         | 0   | 2   | 0x10-0x17 |

|     |          | 1                                                                                                                                         | 1   | 3   | 0x18-0x1F |

| 2   | OV       | 溢出标志<br>该位在下列情况下被置 1:<br>ADD、ADDC 或 SUBB 指令引起符号位变化溢出。<br>MUL 指令引起溢出（结果大于 255）。<br>DIV 指令的除数为 0。<br>ADD、ADDC、SUBB、MUL 和 DIV 指令的其它情况使该位清 0。 |     |     |           |

| 1   | F1       | 用户可定义标志                                                                                                                                   |     |     |           |

| 0   | P        | 奇偶标志。每个指令周期通过硬件设置/清除来表示累加器中 1 的数量的奇偶                                                                                                      |     |     |           |

表 4.4.10 DPS 寄存器

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|------|---|---|---|---|---|---|---|--------|

| Name | - | - | - | - | - | - | - | DPSSEL |

| R/W  | - | - | - | - | - | - | - | R/W    |

| POR  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0      |

| 位 | 字段     | 描述                  |

|---|--------|---------------------|

| 0 | DPSSEL | 0: DPTR<br>1: DPTR1 |

#### 4.4.6 扩展地址寄存器

XRAM 中从 0x40E0 到 0x41FF 的存储器空间为扩展地址寄存器，如下表所示。

表 4.4.11 扩展地址特殊功能寄存器地址映射表

| 地址    | 寄存器  | 地址    | 寄存器      |

|-------|------|-------|----------|

| 40E1H | P0PU | 413FH | DISCOM   |

| 40E2H | P1PU | 4140H | LEDDZ    |

| 40E3H | P2PU | 4141H | BIGDRIVE |

| 40E4H | P3PU | 4150H | ADAN0    |

| 40E5H | P4PU | 4151H | ADAN1    |

| 40E6H | P5PU | 4152H | ADAN2    |

| 40E9H | P0OD | 4153H | ADAN3    |

| 40EAH | P1OD | 4154H | ADAN4    |

| 40EBH | P2OD | 4155H | SEGCR0   |

| 40ECH | P3OD | 4156H | SEGCR1   |

| 40EDH | P4OD | 4157H | SEGCR2   |

| 40EEH | P5OD | 4158H | SEGCR3   |

| 40F1H | P0DB | 4159H | COMCR    |

表 835-11-B4

编号: AiP8F3264-AX-J001

|       |            |       |         |

|-------|------------|-------|---------|

| 40F2H | P1DB       | 415AH | LCMCR0  |

| 40F3H | P2DB       | 415BH | LCMCR1  |

| 40F4H | P4DB       | 415CH | LCMCR2  |

| 4118H | EIPOL0     | 41E2H | T5PWM0E |

| 4119H | EIPOL1     | 41E3H | T5DCR1  |

| 411AH | EINT4SEL   | 41E4H | T5DCR2  |

| 411BH | EINT5SEL   | 41E6H | T5DR0L  |

| 4130H | TKCR       | 41E7H | T5DR0H  |

| 4131H | TKCHSEL    | 41E9H | T5DR1L  |

| 4132H | TKOSCCR    | 41EAH | T5DR1H  |

| 4133H | CTCCR      | 41EBH | T5DR2L  |

| 4134H | TKINT      | 41ECH | T5DR2H  |

| 4135H | TKTMRL     | 41EDH | T5DR3L  |

| 4136H | TKTMRH     | 41EEH | T5DR3H  |

| 4137H | TKDATA1    | 41EFH | T5CR1   |

| 4138H | TKDATAH    | 41F1H | T5DR4L  |

| 4139H | TMR_PLOADL | 41F2H | T5DR4H  |

| 413AH | TMR_PLOADH | 41F3H | T5DR5L  |

| 413BH | LCDCRL     | 41F4H | T5DR5H  |

| 413CH | LDCCRH     | 41F5H | T5DR6L  |

| 413DH | FRASEL     | 41F6H | T5DR6H  |

| 413EH | LEDCR      | 41F7H | T5CR2   |

## 4.5 EEPROM

AiP8F3264 内部有可编程的类 EEPROM 存储器，可操作地址为 0x000~0x3FF。可以由软件使用指令对 EEPROM 存储器进行在系统编程，每次一个字节。一个数据位一旦被清“0”，必须经过擦除才能再回到“1”状态。在进行重新编程之前，一般要将数据字节擦除（置为 0xFF）。

### 4.5.1 EEPROM 区擦除

写 EEPROM 存储器可以清除数据位，但不能使数据位置“1”，只有擦除操作能将 EEPROM 中的数据位置“1”。所以在写入新值之前，必须先擦除待写入的地址。EEPROM 存储器共 1KB，一次擦除操作将擦除整个 EEPROM 区（将 EE 空间所有字节置为 0xFF）。

页擦除的步骤如下：

1. 配置 EEPROM 写入地址寄存器 FSAHR/FSALR (EEPROM 区任意一个地址均可)

2. 配置 EEPROM 写入数据寄存器 FSDR

3. 对 KEYCODE 寄存器依次写入 0x3C、0x02、0xA1 关闭 FSCR 寄存器写保护

4. 使能擦除操作，NOP，NOP，NOP

5. 对 KEYCODE 寄存器写入 0x00 打开 FSCR 寄存器写保护

擦除 EEPROM 区，则可执行下述程序：

```

MOV      FSAHR, #00H

MOV      FSALR, #00H

MOV      FSDR, #00H

MOV      KEYCODE, #3CH

MOV      KEYCODE, #02H

MOV      KEYCODE, #A1H

MOV      FSCR, #24H

NOP

NOP

NOP

MOV      KEYCODE, #00H

```

#### 4.5.2 EEPROM 写入

EEPROM 区一次只能写入一个字节。

用软件对 EEPROM 字节编程的步骤如下：

1. 配置 EEPROM 写入地址寄存器 FSAHR/FSALR（目标地址：0x000~0x3FF）

2. 配置 EEPROM 写入数据寄存器 FSDR（目标地址对应的数据）

3. 对 KEYCODE 寄存器依次写入 0x3C、0x02、0xA1 关闭 FSCR 寄存器写保护

4. 使能写操作，NOP，NOP，NOP

5. 对 KEYCODE 寄存器写入 0x00 打开 FSCR 寄存器写保护

例如要向 0x300H 地址写入一个数据 0x55，则可执行下述程序：

```

MOV      FSAHR, #03H

MOV      FSALR, #00H

MOV      FSDR, #55H

MOV      KEYCODE, #3CH

MOV      KEYCODE, #02H

MOV      KEYCODE, #A1H

MOV      FSCR, #30H

NOP

NOP

NOP

MOV      KEYCODE, #00H

```

#### 4.5.3 EEPROM 读取

EEPROM 存储器可以一次读一个字节，读操作通过 MOVC 指令实现。

用软件对读取 EEPROM 的步骤如下：

1. 配置 EEPROM 写入地址寄存器 FSAHR/FSALR（目标地址：0x000~0x3FF）

2. 对 KEYCODE 寄存器依次写入 0x3C、0x02、0xA1 关闭 FSCR 寄存器写保护

3. 使能读操作

4. 对 KEYCODE 寄存器写入 0x00 打开 FSCR 寄存器写保护

例如读取 0x300H 地址的数据，则可执行下述程序：

```

#include <absacc.h>

FSAHR =0x30;

FSALR =0x00;

KEYCODE =0x3C;

KEYCODE =0x02;

KEYCODE =0xA1;

FSCR |=0x20;

FSCR |=0x08;

dat =CBYTE[0x300];

KEYCODE =0x00;

```

## 5 时钟

### 5.1 特性

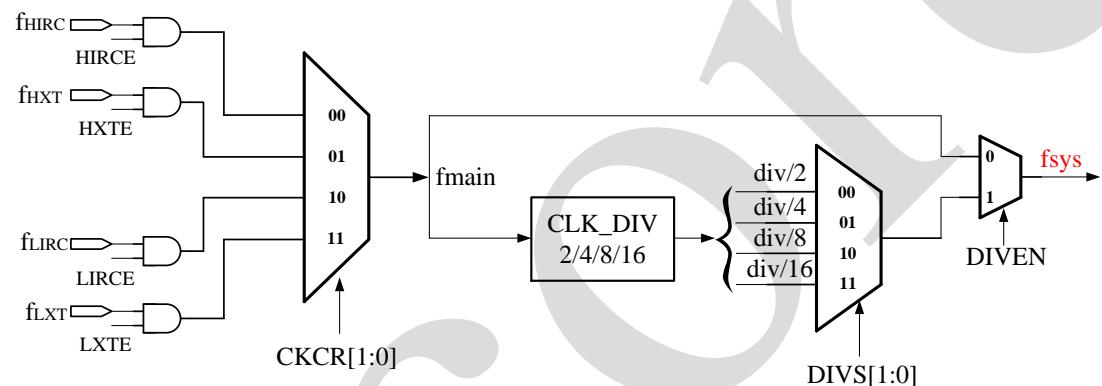

时钟发生器为内核和外围设备提供时钟，包括晶体振荡器 HXT/LXT 和内部 HIRC/LIRC 振荡器。主时钟默认为 HIRC (16MHz)。

- 内部高速振荡 (HIRC)

- 内部低速振荡 (LIRC)

- 外部高速晶振 (HXT)

- 外部低速晶振 (LXT)

### 5.2 功能框图

图 5.2.1 时钟功能框图

### 5.3 寄存器列表

表 5.3.1 时钟寄存器列表

| 寄存器名称  | 地址  | 描述              | 初值  |

|--------|-----|-----------------|-----|

| OSCCR  | C8H | 振荡时钟控制寄存器       | 10H |

| OSCCR1 | F6H | 晶振控制寄存器         | 00H |

| OSCTS  | F7H | 外部晶振稳定检测时间控制寄存器 | FFH |

| CKCR   | F5H | 系统时钟控制寄存器       | 10H |

## 5.4 寄存器说明

表 5.4.1 OSCCR 寄存器

| Bit  | 7    | 6     | 5    | 4     | 3 | 2     | 1          | 0   |

|------|------|-------|------|-------|---|-------|------------|-----|

| Name | LXTE | LIRCE | HXTE | HIRCE | — | DIVEN | DIVS[1: 0] |     |

| R/W  | R/W  | R/W   | R/W  | R/W   | — | R/W   | R/W        | R/W |

| POR  | 0    | 0     | 0    | 1     | 0 | 0     | 0          | 0   |

| 位   | 字段        | 描述                                                        |

|-----|-----------|-----------------------------------------------------------|

| 7   | LXTE      | LXT 时钟使能<br>0: LXT 使能关闭<br>1: LXT 使能打开                    |

| 6   | LIRCE     | LIRC 时钟使能<br>0: LIRC 时钟使能关闭<br>1: LIRC 时钟使能打开             |

| 5   | HXTE      | HXT 时钟使能<br>0: HXT 时钟使能关闭<br>1: HXT 时钟使能打开                |

| 4   | HIRCE     | HIRC 时钟使能<br>0: HIRC 时钟使能关闭<br>1: HIRC 时钟使能打开             |

| 3   | 保留        |                                                           |

| 2   | DIVEN     | 系统时钟分频使能<br>0: 除能<br>1: 使能                                |

| 1-0 | DIVS[1:0] | 系统时钟分频选择<br>00: 2 分频<br>01: 4 分频<br>10: 8 分频<br>11: 16 分频 |

表 5.4.2 OSCCR1 寄存器

| Bit  | 7       | 6   | 5   | 4   | 3           | 2   | 1        | 0        |

|------|---------|-----|-----|-----|-------------|-----|----------|----------|

| Name | PAD_SEL | —   | —   | —   | LXT_QKUP_EH | —   | LXT_STBF | HXT_STBF |

| R/W  | W/R     | W/R | W/R | W/R | R/W         | R/W | R/W      | R/W      |

| POR  | 0       | 0   | 0   | 1   | 0           | 0   | 0        | 0        |

| 位 | 字段      | 描述                                      |

|---|---------|-----------------------------------------|

| 7 | PAD_SEL | 外部振荡端口复用使能控制位<br>1: 外部振荡端口复用<br>0: 禁止复用 |

# 无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

表 835-11-B4

编号: AiP8F3264-AX-J001

|     |             |                                                                            |

|-----|-------------|----------------------------------------------------------------------------|

| 6-4 | 保留          |                                                                            |

| 3   | LXT_QKUP_EH | LXT 快速起振使能位, 起振后约 2s 可选进入低功耗模式<br>1: 使能<br>0: 不使能                          |

| 2   | 保留          |                                                                            |

| 1   | LXT_STBF    | LXT 振荡稳定标志位<br>1: LXT 振荡稳定计数器计数至 OSCTS 设定值<br>0: LXT 振荡稳定计数器未计数至 OSCTS 设定值 |

| 0   | HXT_STBF    | HXT 振荡稳定标志位<br>1: HXT 振荡稳定计数器计数至 OSCTS 设定值<br>0: HXT 振荡稳定计数器未计数至 OSCTS 设定值 |

表 5.4.3 时钟配置方式表

| PAD_SEL | lxte | hxte | LXT | HXT | P50/P51 | P53/P54 |

|---------|------|------|-----|-----|---------|---------|

| 0       | 0    | 0    | 不使能 | 不使能 | IO      | IO      |

| 0       | 0    | 1    | 不使能 | 使能  | 高振端口    | IO      |

| 0       | 1    | 0    | 使能  | 不使能 | IO      | 低振端口    |

| 0       | 1    | 1    | 使能  | 使能  | 高振端口    | 低振端口    |

| 1       | 0    | 0    | 不使能 | 不使能 | IO      | IO      |

| 1       | 0    | 1    | 不使能 | 使能  | 高振端口    | IO      |

| 1       | 1    | 0    | 使能  | 不使能 | 低振端口    | IO      |

| 1       | 1    | 1    | 使能  | 不使能 | 低振端口    | IO      |

表 5.4.4 OSCTS 寄存器

| Bit  | 7   | 6   | 5   | 4   | 3      | 2      | 1      | 0      |

|------|-----|-----|-----|-----|--------|--------|--------|--------|

| Name | —   | —   | —   | —   | OSCTS3 | OSCTS2 | OSCTS1 | OSCTS0 |

| R/W  | R/W | R/W | R/W | R/W | R/W    | R/W    | R/W    | R/W    |

| POR  | 1   | 1   | 1   | 1   | 1      | 1      | 1      | 1      |

| 位   | 字段          | 描述                                                                                                                                                                                                         |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | 保留          |                                                                                                                                                                                                            |

| 3-0 | OSCTS[3: 0] | OSCTS 振荡稳定时间选择<br>0000: 2^8/fsys<br>0001: 2^9/fsys<br>0010: 2^10/fsys<br>0011: 2^11/fsys<br>0100: 2^12/fsys<br>0101: 2^13/fsys<br>0110: 2^14/fsys<br>1011: 2^15/fsys<br>1000: 2^16/fsys<br>1001: 2^17/fsys |

|  |  |                                  |

|--|--|----------------------------------|

|  |  | 1010: 2^18/fsys<br>其他: 2^18/fsys |

|--|--|----------------------------------|

表 5.4.5 CKCR 寄存器

| Bit  | 7    | 6     | 5    | 4     | 3   | 2   | 1          | 0   |

|------|------|-------|------|-------|-----|-----|------------|-----|

| Name | LXTF | LIRCF | HXTF | HIRCF | —   | —   | CKCR[1: 0] |     |

| R/W  | R    | R     | R    | R     | R/W | R/W | R/W        | R/W |

| POR  | 0    | 0     | 0    | 1     | 0   | 0   | 0          | 0   |

| 位   | 字段         | 描述                                                                  |

|-----|------------|---------------------------------------------------------------------|

| 7   | LXTF       | LXT 作为系统时钟标志位<br>1: LXT 为系统时钟源                                      |

| 6   | LIRCF      | LIRC 作为系统时钟标志位<br>1: LIRC 为系统时钟源                                    |

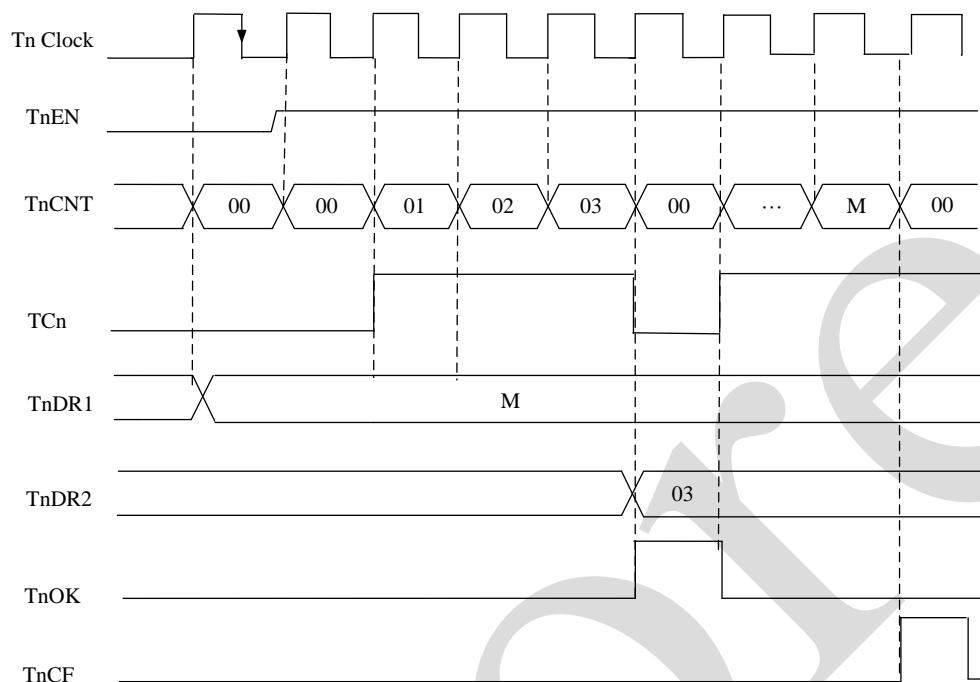

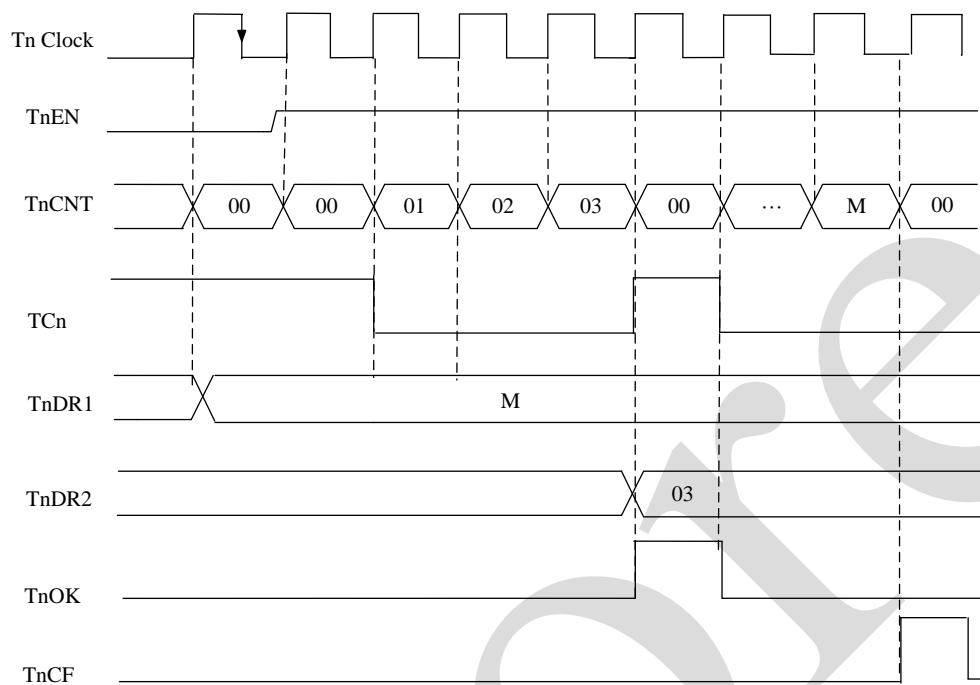

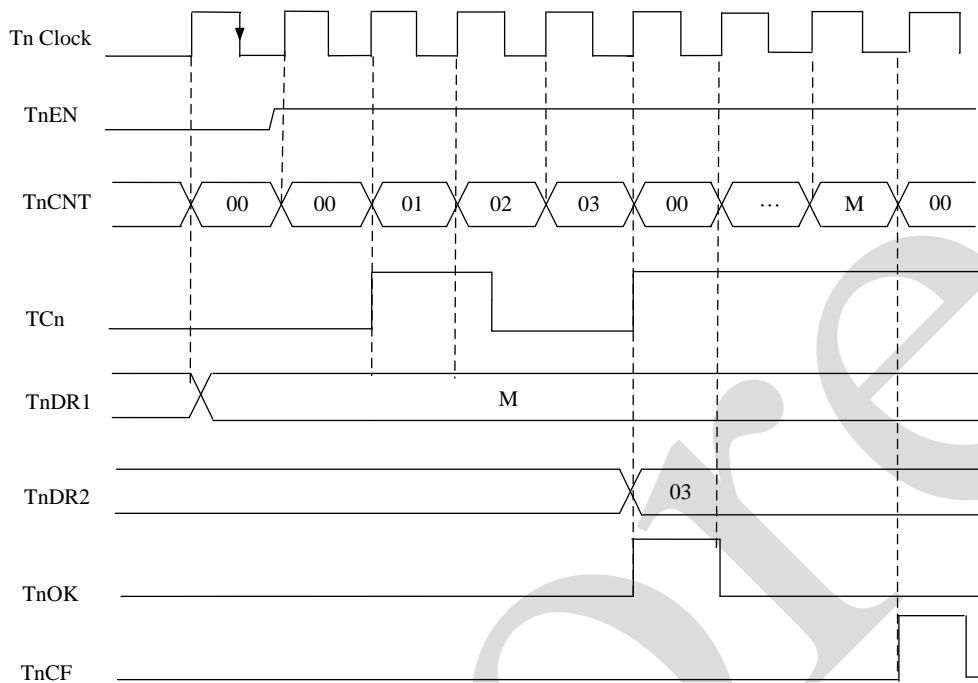

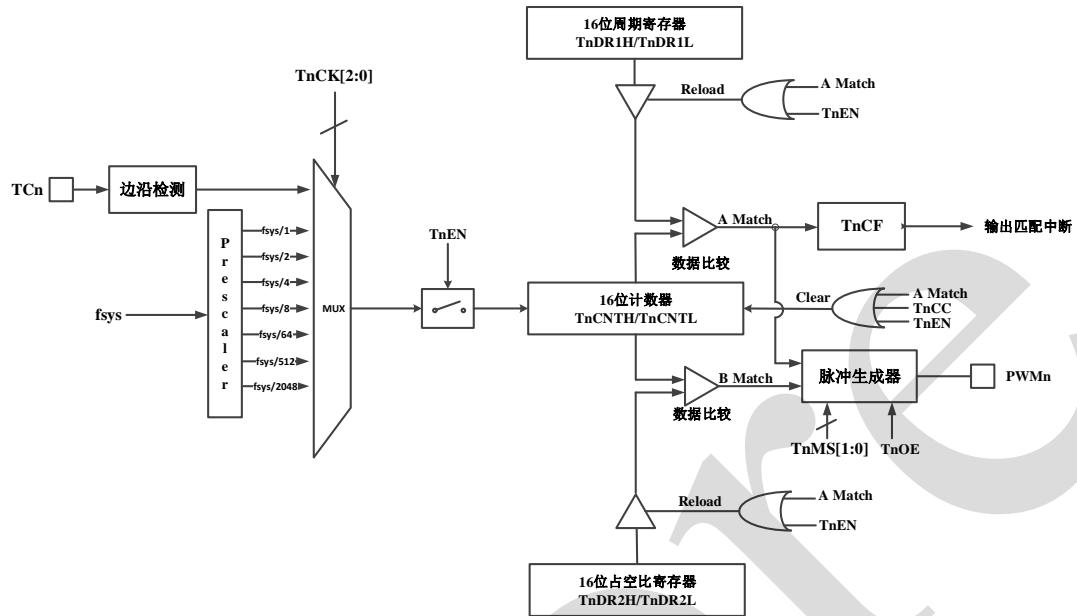

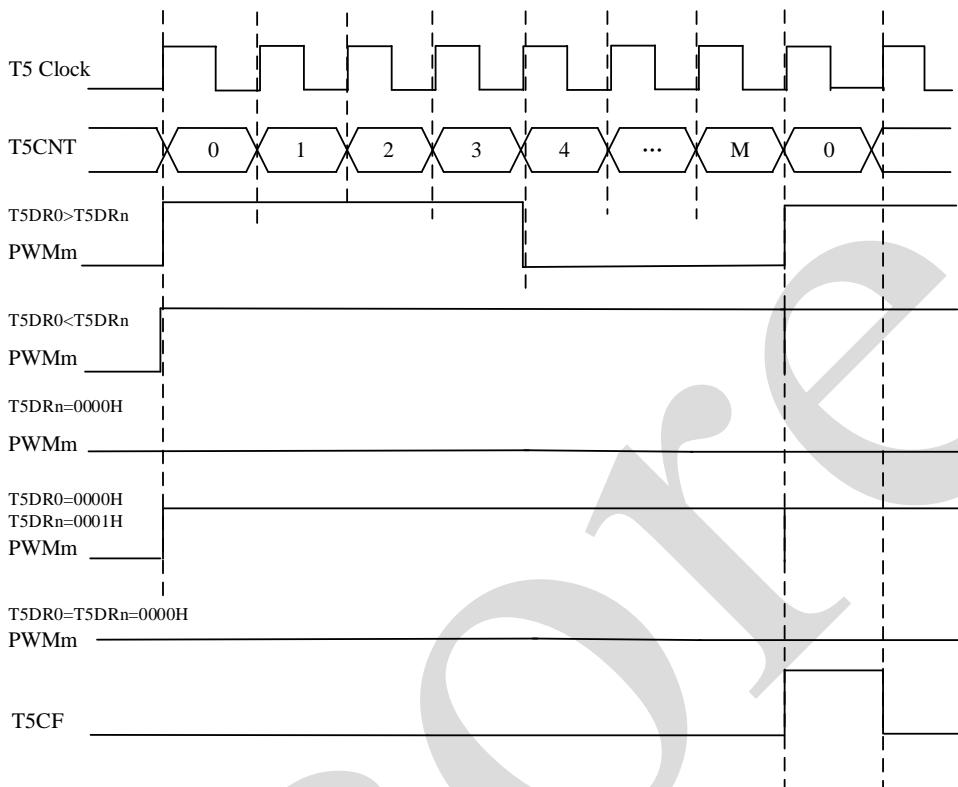

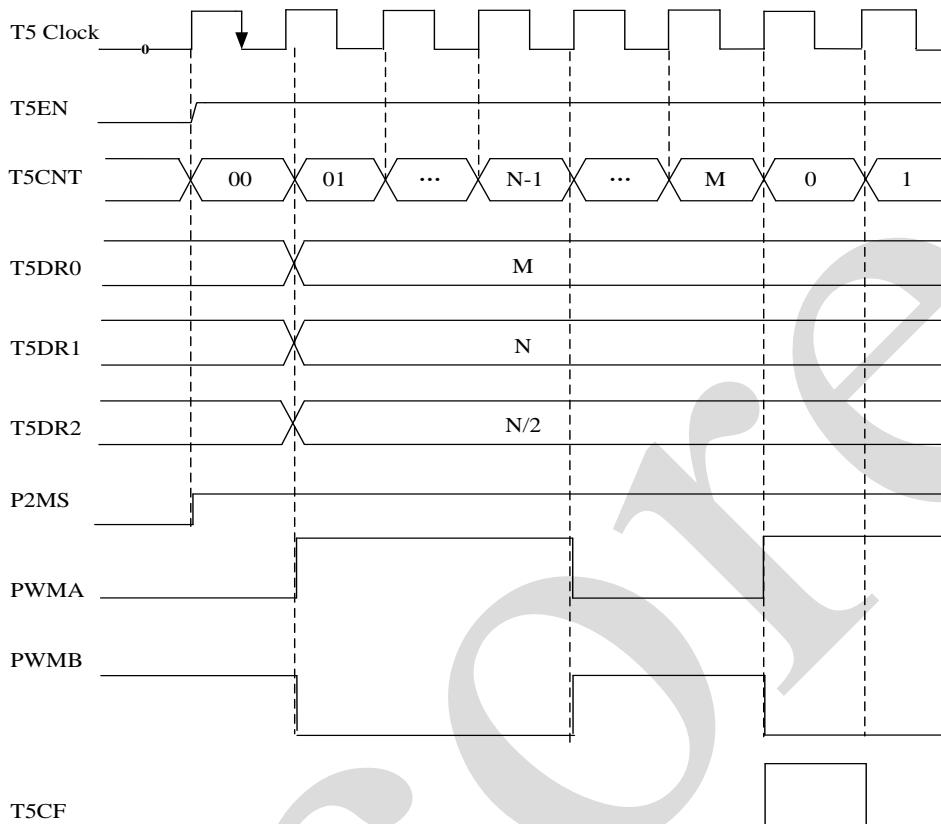

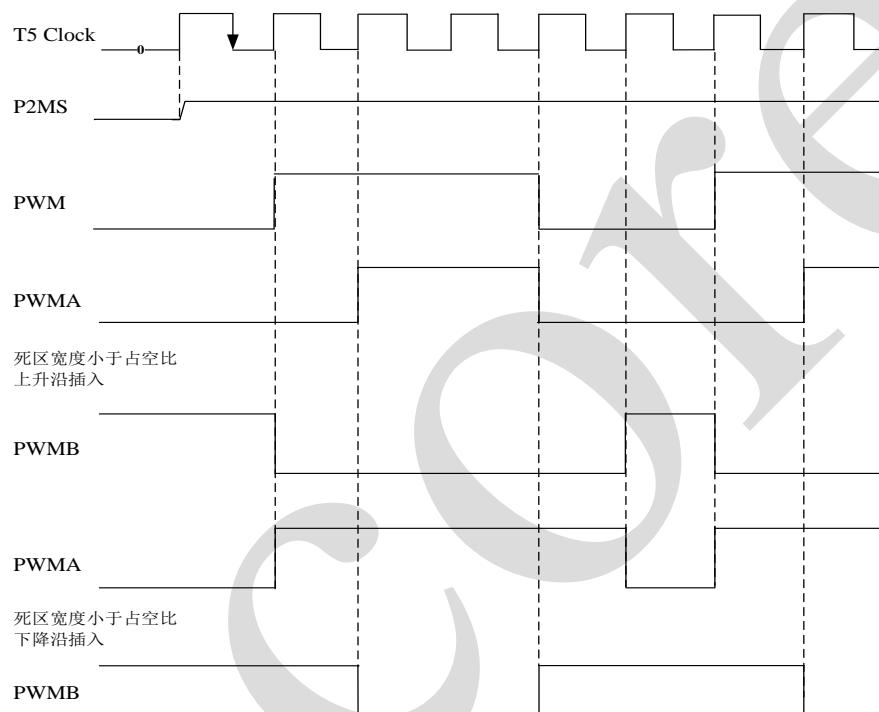

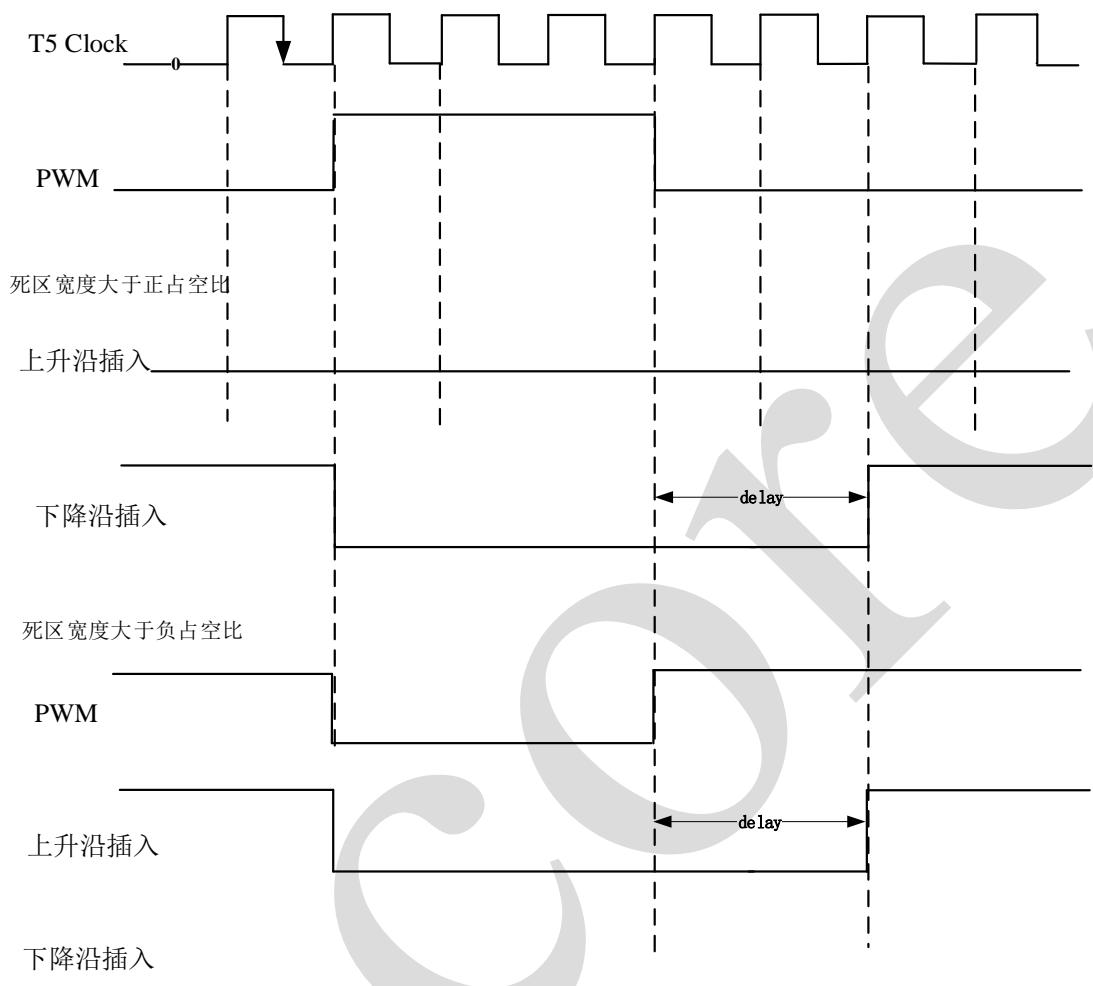

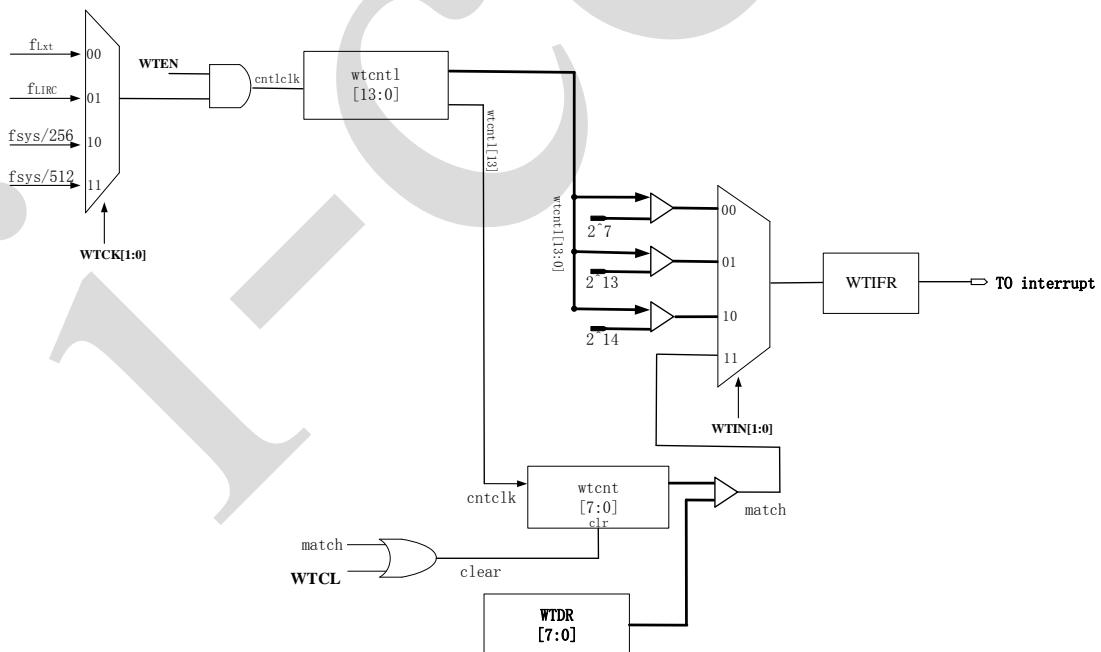

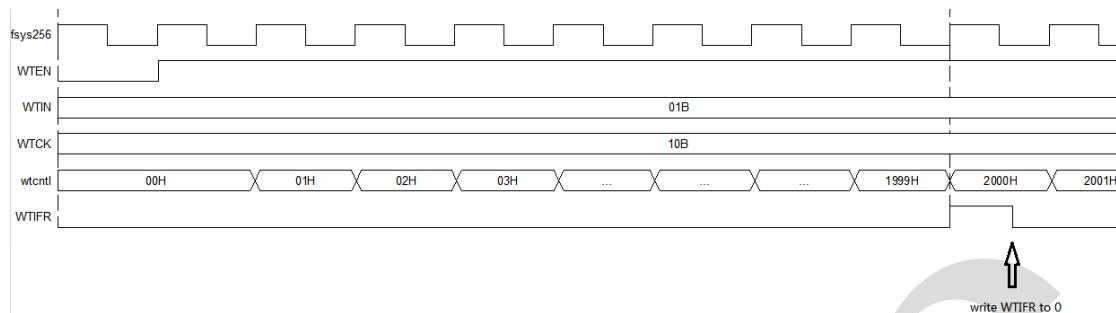

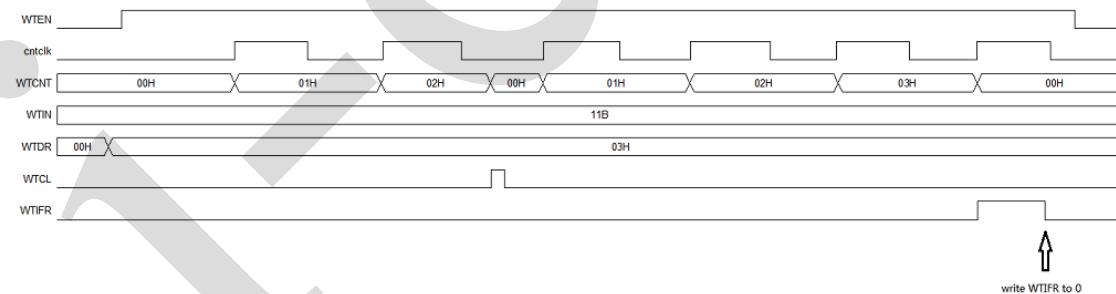

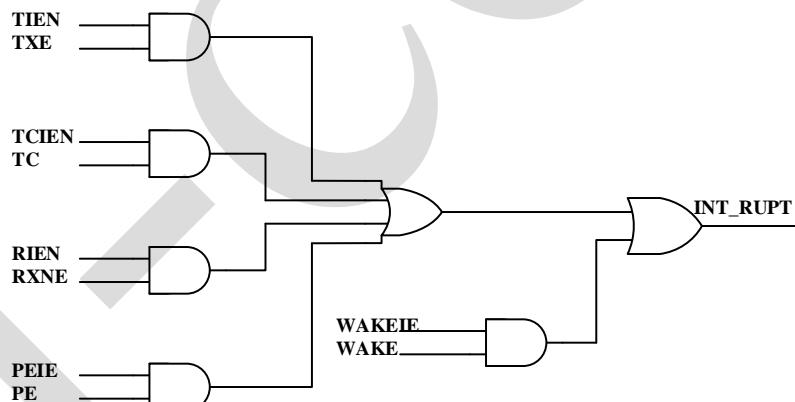

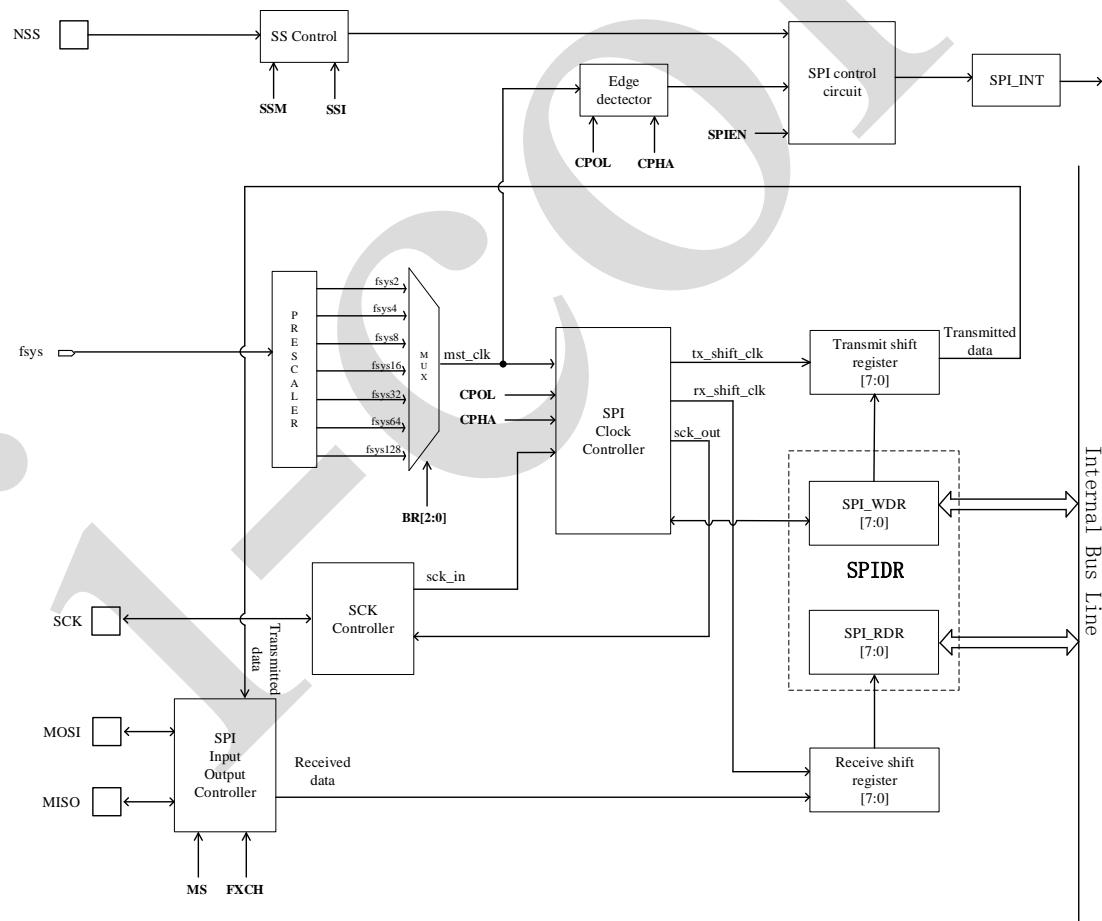

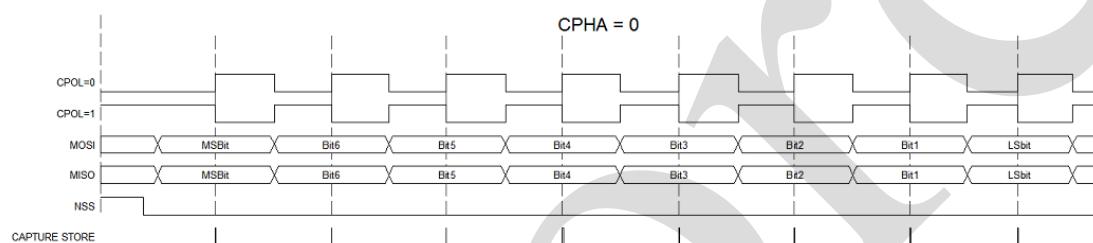

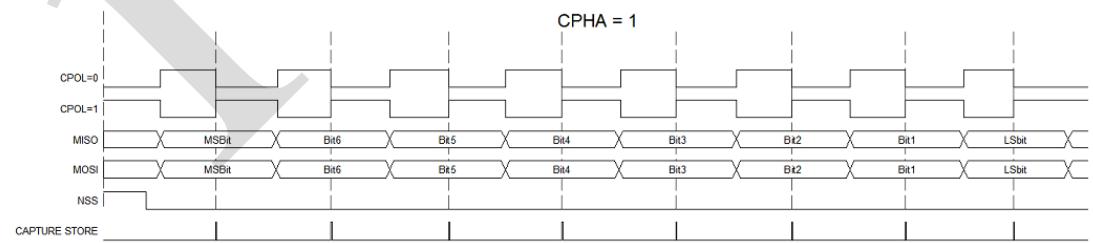

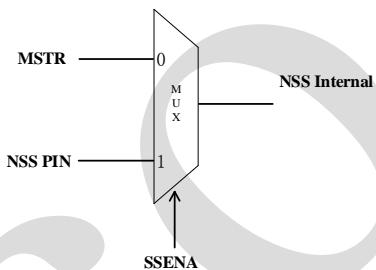

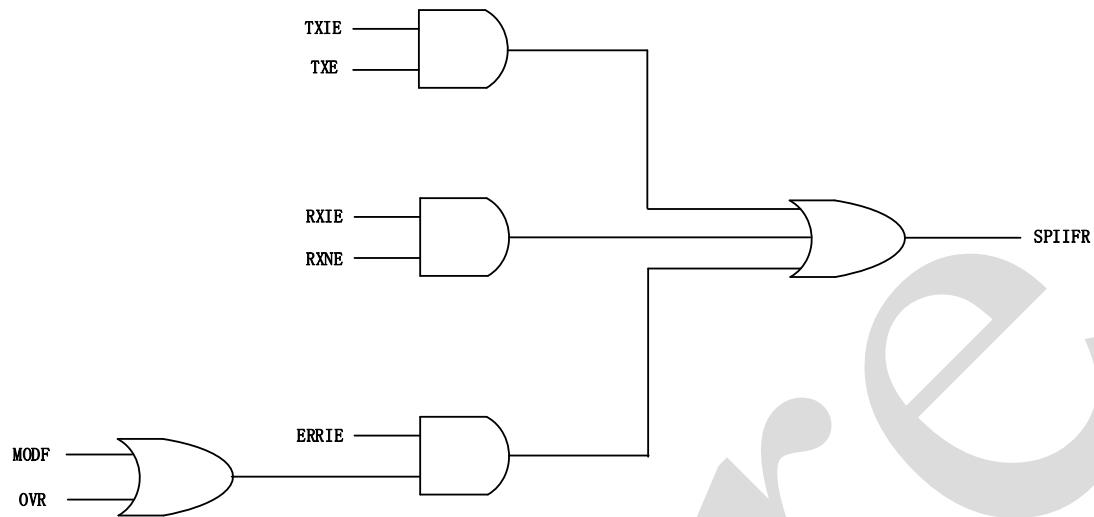

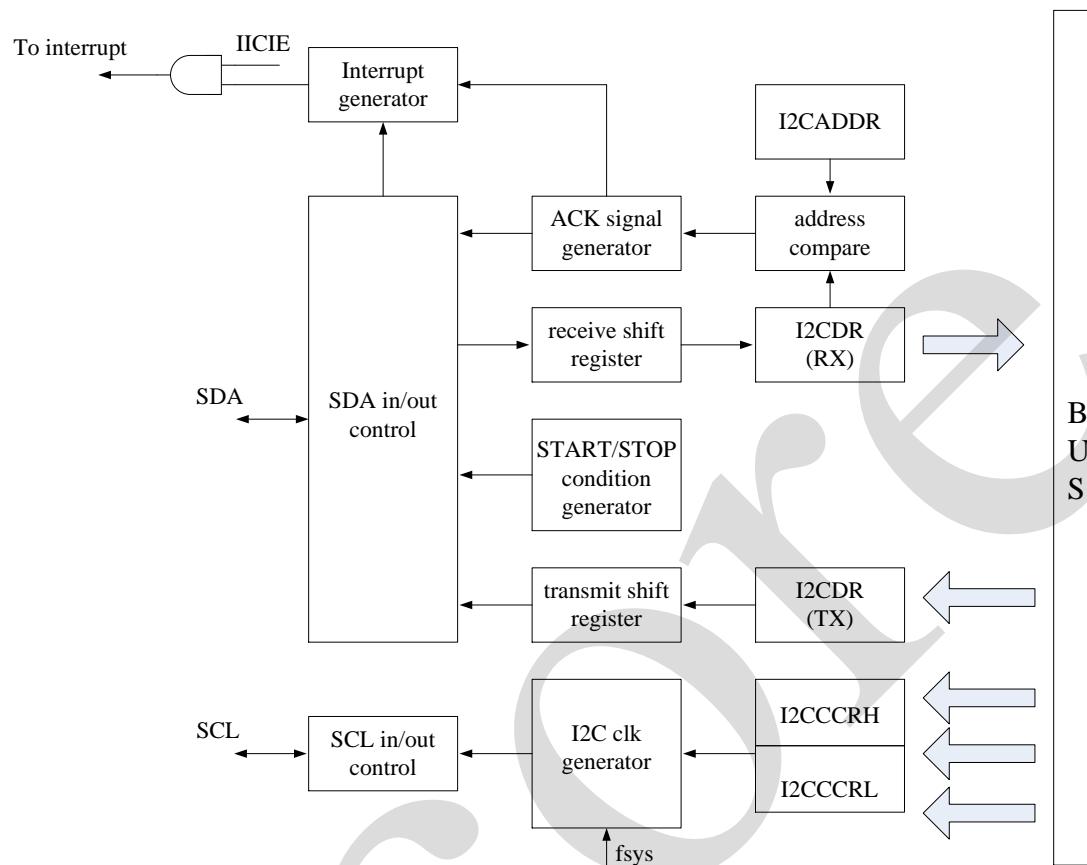

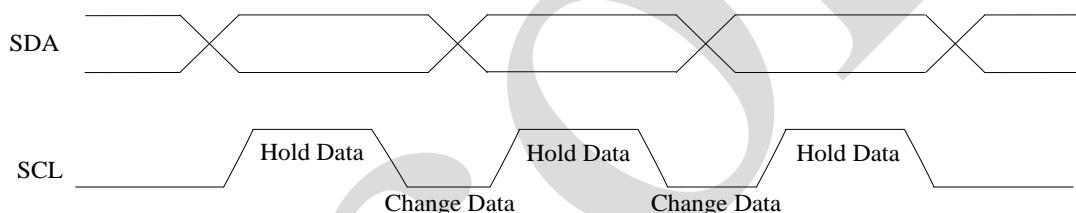

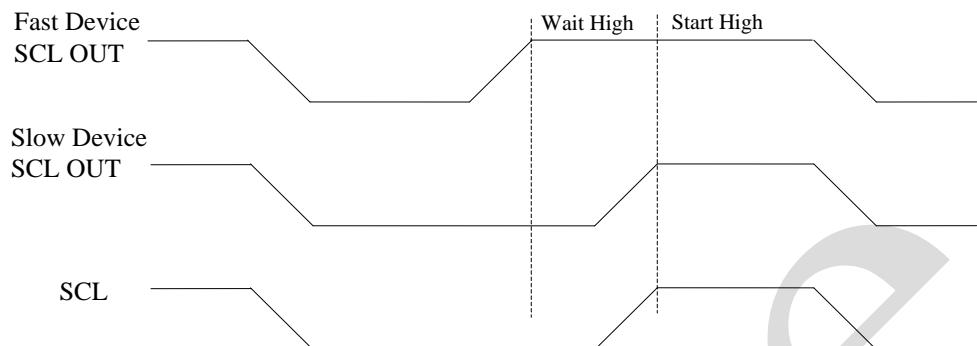

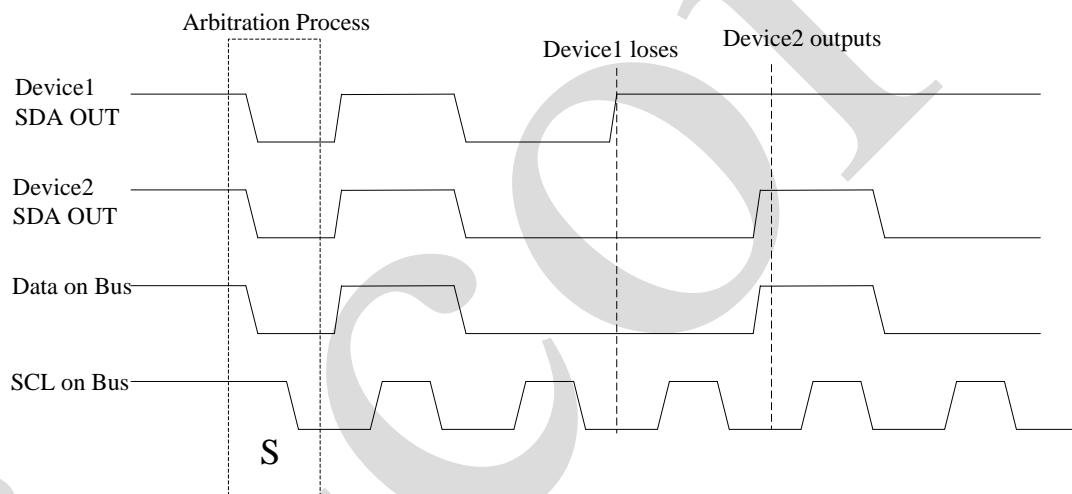

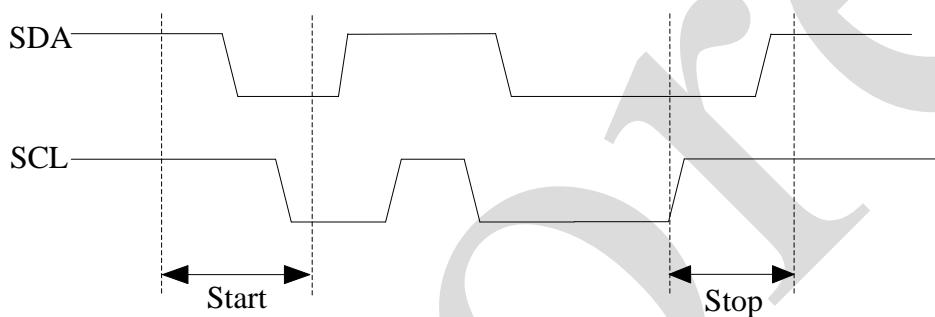

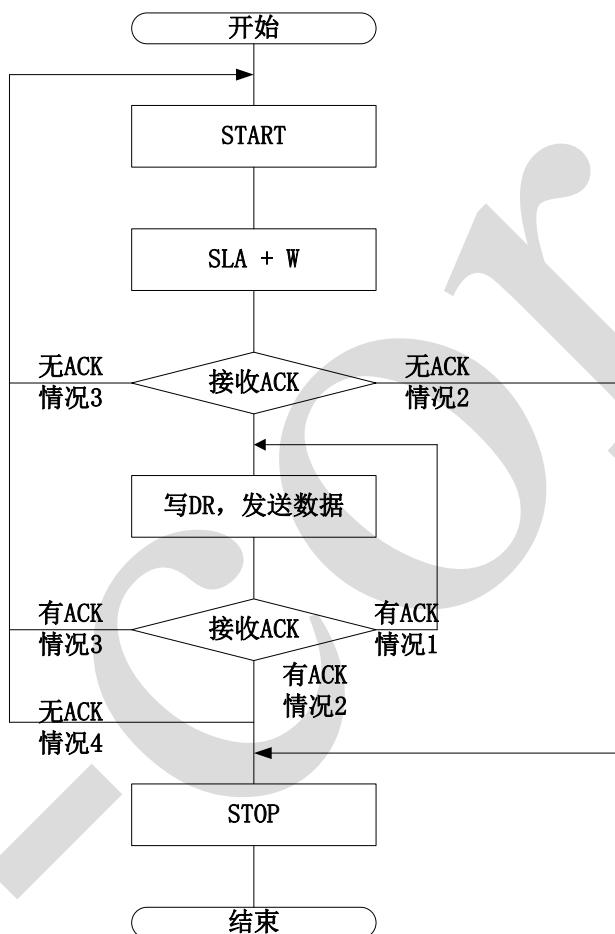

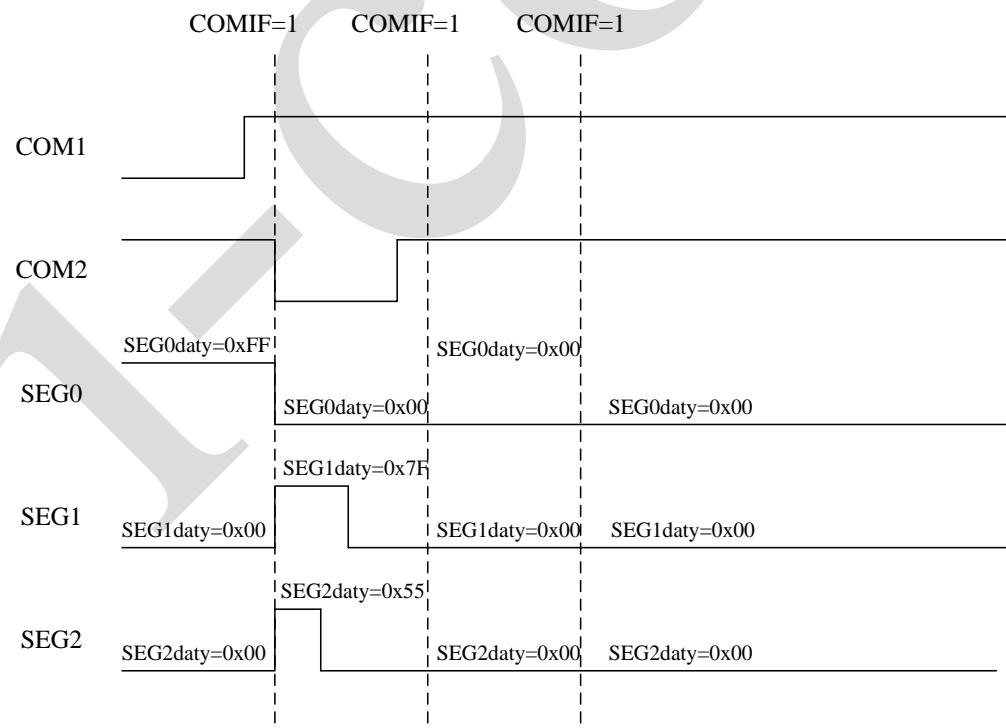

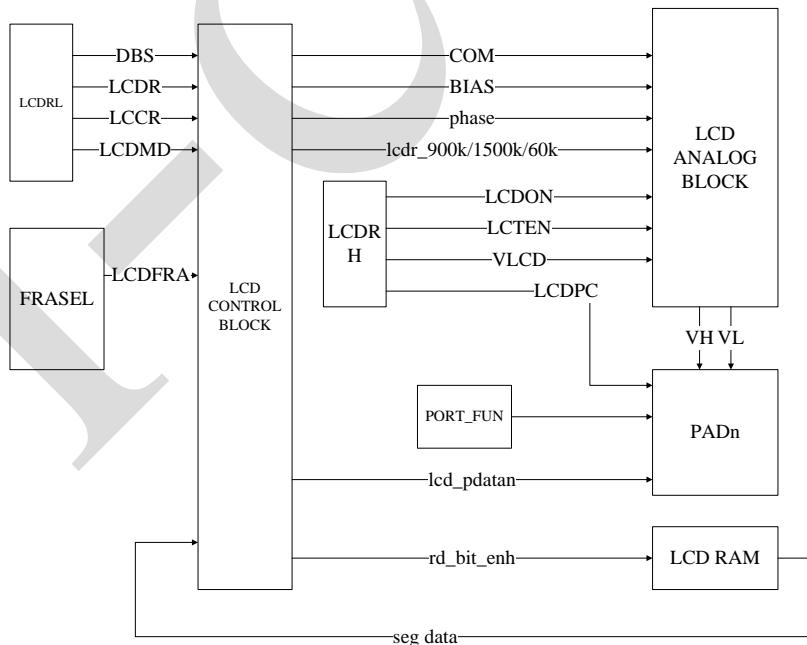

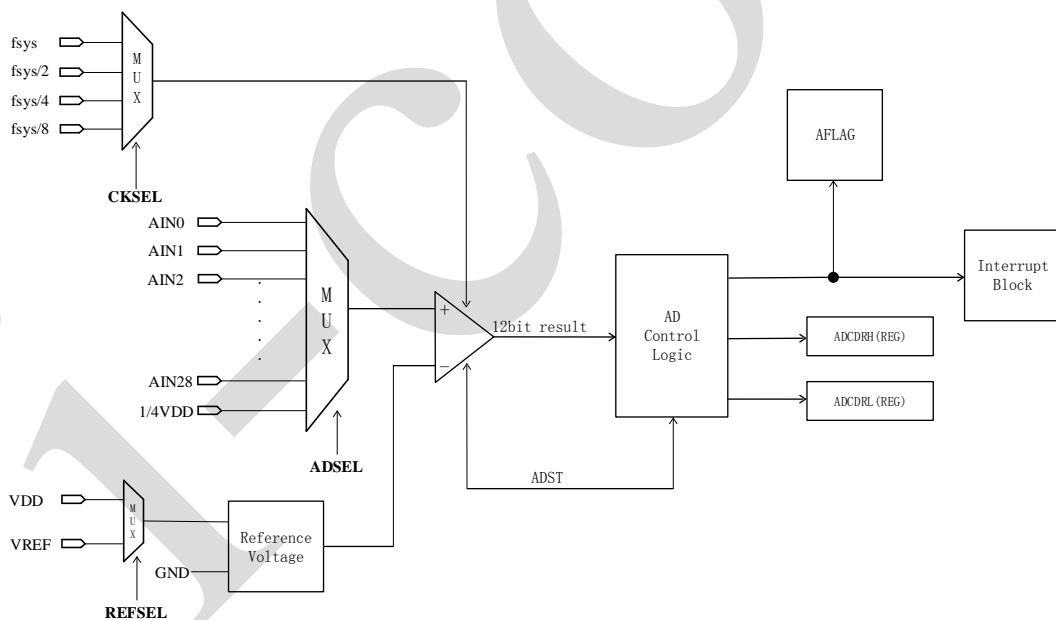

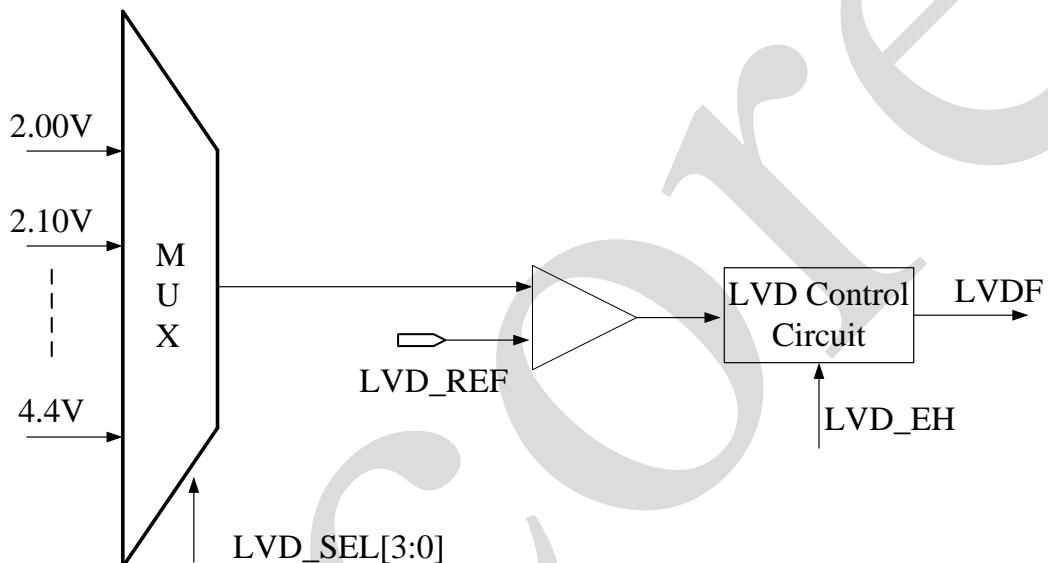

| 5   | HXTF       | HXT 作为系统时钟标志位<br>1: HXT 为系统时钟源                                      |